# Kapitel 5

# CMOS-Bildsensorlösungen für Hochgeschwindigkeitsbildaufnahmen

In diesem Kapitel sollen zwei unterschiedliche Konzepte zur Realisierung zweidimensionaler CMOS-Bildsensoren für Hochgeschwindigkeitsanwendungen präsentiert werden. Die ausgewählten Schaltkreise sollen dabei die Vorteile der CMOS- gegenüber der CCD-Technologie ausnutzen und die vorgestellten Erkenntnisse über die Grundlagen der schnellen Bildsensorik für den Schaltungsentwurf verwenden. So wird die Auswahl der Pixelstruktur nach den Überlegungen aus dem vorherigen Kapitel getroffen und für die entwickelten integrierten Lösungen eingesetzt. Für die ausgesuchten Konzepte werden die geeignetsten Ausleseschaltungen und On-Chip-Signalverarbeitung sorgfältig ausgesucht und passend zu der Anwendung optimiert. Die vorgeschlagenen und anschließend realisierten Bildsensorlösungen sollen den Weg für den Einsatz der CMOS-Technik in der Hochgeschwindigkeitskinematographie aufzeigen.

Aus den vorgestellten Diskussionen im vierten Kapitel über die Bildelemente bei CMOS-Bildsensoren, die die Vor- und Nachteile einzelner Strukturen charakterisieren, wird im folgenden für die angestrebten 2D-CMOS-Bildsensoren das vorgestellte einfache Pixel mit synchronem elektronischen Shutter im Standard-Modus verwendet. Damit wird der bessere Füll-Faktor, das günstigere Signal-Rausch-Verhältnis und der höhere Dynamikbereich gegenüber den anderen vorgestellten Pixelstrukturen ausgenutzt. Eine durch die Differenz der Bilddauer und der Auslesezeit bestimmte Integrationsdauer wird nicht als eine Einschränkung, sondern aufgrund der bei kürzeren Integrationszeiten schlechteren Empfindlichkeit und den ausgeprägten parasitären Effekten (Blooming und Smearing) als eine Herausforderung gesehen. Angestrebte Integrationszeiten im unteren Mikrosekunden-  $(1 \,\mu\text{s} - 150 \,\mu\text{s})$  bis hinab in den Nanosekundenbereich sind nicht nur für Standard-Hochgeschwindigkeitskinematographie sehr interessant, sondern sie eröffnen auch neue Möglichkeiten der CMOS-Bildsensorik für die optische Meßtechnik.

Diesen groben Überlegungen folgend sollen zwei unterschiedliche CMOS-Bildsensoren bezüglich der Ausleseverfahren, der Handhabung vom Rauschen, der notwendigen On-Chip-Signalverarbeitung und der Bildverbesserung vorgestellt werden.

# 5.1 Das schnelle CMOS-Sensorsystem mit externer Bildverbesserung

Die angestrebte Zielsetzung der erst hier vorgestellten Schaltung war ein Nachweis für den Einsatz der CMOS-Schaltungstechnik in der Hochgeschwindigkeits-Bildsensorik. Der als erste Testchip in 1  $\mu$  m Standard-CMOS-Prozeß realisierte CMOS-Bildsensor soll daher bei einer Auflösung von 128 × 128 Pixel die Bildaufnahme bei Bildwiederholraten von mehr als 1000 Bilder/s und Integrationszeiten in unteren Mikrosekundenbereich (1 - 150  $\mu$  m) ermöglichen. Der Bildsensor muß außerdem eine mit Hilfe des elektronischen Shutters innerhalb der Pixel verzerrungsfreie und von Blooming und Smearing-Effekten unabhängige Bildakquisition gewährleisten. Aufgrund der angestrebten Anwendung für die Hochgeschwindigkeitsaufnahmen, die üblicherweise unter gut definierten Beleuchtungsverhältnissen stattfinden, waren ein DR von 60 dB bzw. ein SNR von mehr als 45 dB als Ziel gesetzt.

#### 5.1.1 Motivation

Um eine hohe Pixel- und damit verknüpfte Bildwiederholrate zu erreichen, wird ein Stromauslesemodus verwendet, um die Signale aus den Pixeln auszulesen. Dieses Ausleseverfahren wird bei den Standard-Anwendungen mit CMOS-Bildsensorik nicht oft angewendet, da für seine sehr gute Treibereigenschaften ein höheres FPN in Kauf genommen werden muß [87, 88].

Das Stromausleseverfahren wurde bei dieser Anwendung gewählt, weil damit eine schnelle Übertragung der Signalinformation in Form des Stromes aus den Pixeln trotz der hohen parasitären Kapazitäten an den Spaltenleitungen gewährleistet ist. Für eine effiziente Auslese in der Umgebung dieser hohen Kapazitäten ist ein Transimpedanzverstärker entwickelt worden, der N mal in einer organisierten Verstärkerbank am Ende jeder Spalte eingesetzt ist. Um die notwendig kurzen Einschwingzeiten zu ermöglichen, wird der Verstärker mit einem niederohmigen Eingang und einem zusätzlichen Mechanismus versehen, der die Spaltenleitung auf einem konstanten Potential hält.

Das durch die Natur der Stromauslese verursachte FPN ist näher untersucht und Maßnahmen zu seiner Aufhebung sind vorgeschlagen worden. Dabei werden keine On-Chip-Lösungen gesucht, sondern es werden softwaretechnische Maßnahmen durch die Entwicklung eines einfachen Algorithmus ergriffen.

#### 5.1.2 Schaltungstechnische Realisierung

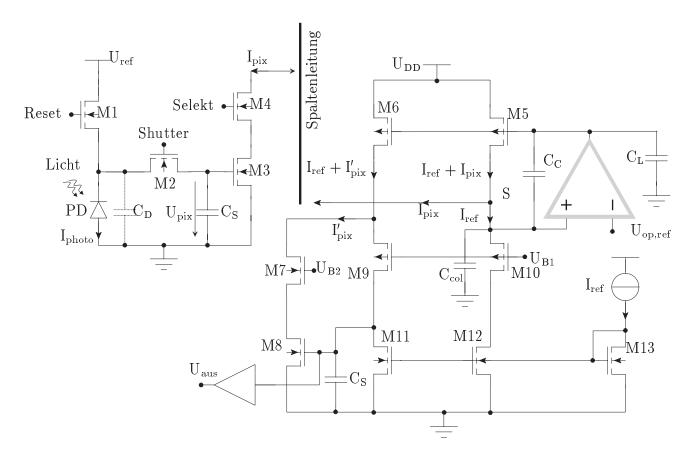

Den Grundkern eines CMOS-Bildsensors stellen die eingesetzte Pixelstruktur und die spaltenweise organisierten Ausleseschaltungen dar. Die Abbildung 5.1 zeigt das Pixel mit elektronischem Shutter, das für die Stromauslese eine Transkonduktanzstufe (oder Source-Schaltung) und eine für die Auslese der Signalwerte aus dem Pixel entwickelte Stromausleseschaltung verwendet. Wie schon vorher beschrieben, wird bei einem Pixelbetrieb im Standard-Modus nach dem Zurücksetzen des Pixels und einer abgeschlossenen Integration mittels des Shuttertransistors der Speicherkondensator vom Einfluß der weiteren unerwünschten Belichtung entkoppelt. Somit liegt auf dem Speicherkondensator  $C_S$  die gespeicherte Spannung für eine zeilenweise durchgeführte Auslese bereit. Die Abwicklung dieser Vorgänge wird mittels zwei globaler, für alle Pixel jeweils gleichen Signale ("Reset"- und "Shutter"-Signal) ermöglicht, was zu einer synchronen Beleuchtung der gesamten photoempfindlichen Fläche führt. Wenn das Pixel über den Selekttransistor M4 zeilenweise angewählt ist, wird über den Transkonduktanzverstärker M3 die im Pixel gespeicherte Spannung in den Ausgangsstrom  $I_{pix}$  konvertiert und somit die Signalinformation aus der photoempfindlichen Matrix ausgelesen. Das Zeitdiagramm der beschriebenen Steuersignale für das verwendete einfache Pixel mit elektronischem Shutter im Standard-Modus ist in Abbildung 4.9 zu finden.

An dem Knoten S der Spaltenleitung wird der Strom  $I_{pix}$  zum Referenzstrom  $I_{ref}$ , der durch den Transistor M10 fließt, aufaddiert. Der resultierende Strom  $I_{pix} + I_{ref}$  fließt durch den Transistor M5 bzw. M6, falls die beiden Transistoren gut matchen und in Sättigung arbeiten. Da aufgrund des Stromspiegels M11-M12-M13 der Referenzstrom  $I_{ref}$  im Transistor M9 fließt, wird der Zweig, in dem sich die Transistoren M7 und M8 befinden, von dem Strom  $I'_{pix} = I_{pix}$  durchflossen. Falls die Transistoren M3 und M8 die gleiche Geometrie besitzen und gut matchen und zudem der Speicherkondensator  $C_S$  am Ausgang der Schaltung nachgebildet ist, entsteht am Ausgang der Schaltung eine Spannung  $U_{pix}$  entspricht.

Um trotz einer an der Spaltenleitung existierenden hohen parasitären Kapazität  $C_{col}$  kurze Einschwingzeiten zu erreichen, wird die Zeitkonstante an dem Knoten S mittels einer kleinen Eingangsimpedanz der Gate-Schaltung M10 möglichst niedrig gehalten. Zusätzlich dient der verwendete Operationsverstärker dazu, den Knoten S an einem konstanten Potential zu halten, indem er durch eine ausreichend hohe Verstärkung seine Eingangsspannung auf Null regelt. (Somit liegt die Spaltenleitung auf dem Potential  $U_{op,ref}$ ).

Beim Entwurf des Pixels ist neben allen im Kapitel 3.3.1 beschriebenen Maßnahmen für Blooming-, Smearing-Unterdrückung, usw. (beispielsweise eine gute Lichtabschirmung der kritischen Bauelemente) besonders auf die Dimensionierung des Transkonduktanzverstärkers zu achten. Angesichts eines hohen Füll-Faktors ist der Speicherkondensator  $C_S$  hauptsächlich durch die parasitären Transistorkapazitäten zu realisieren. Eine etwas größere als die

Abbildung 5.1: Pixel mit synchronem elektronischen Shutter und Stromausleseschaltung.

minimale Geometrie des Transkonduktanzverstärkers gewährleistet aufgrund eines höheren Kapazitätsbelags seiner parasitären Kapazitäten bei einer vorgegebenen Fläche einen vergleichsweise höheren Kapazitätswert als ein konventionelles analoges CMOS-Kondensator-Bauelement. Bei der Wahl der Geometrie des Transkonduktanzverstärkers ist darauf zu achten, daß mit seiner Steilheit nicht zu hohe Ausgangsströme ausgelöst werden, die aufgrund der Länge N der angewählten Zeile in einer zu hohen Verlustleistung resultieren können. Ebenso ist auf das Rauschverhalten (siehe Kapitel 5.1.4) und auf den resultierenden Füll-Faktor des Pixels zu achten.

# 5.1.3 Statische Übertragungsfunktion und "Matching"-Verhalten

Bei der Berechnung der angestrebten linearen Übertragungskennline vom Speicherkondensator im Pixel bis zum Ausgang des beschriebenen Spalten-Transimpedanz (I-V)-Verstärkers ist zu beachten, daß alle Transistoren in der gezeigten Schaltung bis auf die verwendeten Schalter M4 und Transistor M7, der den geschlossenen Schalter M4 nachbildet, in Sättigung arbeiten und sehr gute "Matching"-Eigenschaften aufweisen. Dennoch wird der Einfluß von "Mismatch" aufgrund von Prozeßschwankungen nicht nur zur Berechnung der Übertra-

gungsfunktion, sondern vor allem zur Berechnung des FPN berücksichtigt.

Unter Annahme, daß der Einfluß der Transistoren M9-M13 vernachlässigt wird, d.h. die gelieferten Referenzströme  $I_{ref}$  sehr gut matchen, werden zur Berechnung der Übertragungsfunktion die Einflüsse der Transistoren M5 und M6, bzw. M3 und M8 gemäß folgender Knotengleichungen berücksichtigt. Gemäß der Kennlinie des MOS-Transistors in Sättigung (siehe Anhang A) folgt aus

$$I_5 = \frac{\beta_p}{2} \frac{W_5}{L_5} (U_{GS,5} - U_{t,5})^2 = \frac{\beta_n}{2} \frac{W_8}{L_8} (U_{GS,8} - U_{t,8})^2 + I_{ref}$$

(5.1)

und

$$I_6 = \frac{\beta_p}{2} \frac{W_6}{L_6} (U_{GS,6} - U_{t,6})^2 = \frac{\beta_n}{2} \frac{W_3}{L_3} (U_{GS,3} - U_{t,3})^2 + I_{ref}$$

(5.2)

mit den Annahmen, daß  $U_{GS,5}=U_{GS,6}$  und  $U_{GS,3}=U_{CS}=U_{ref}-U_{int}$  bzw.  $U_{GS,8}=U_{aus}$  gilt, die Ausgangsspannung

$$U_{aus} = \sqrt{\frac{W_5 L_8 \beta_p}{L_5 W_8 \beta_n}} \left( \sqrt{\frac{W_3 L_6 \beta_n}{L_3 W_6 \beta_p}} \left( U_{ref} - U_{int} - U_{t,3} \right) + U_{t,6} - U_{t,5} \right) + U_{t,8}.$$

(5.3)

Dabei sind  $\beta_n$  und  $\beta_p$  Verstärkungsfaktoren des PMOS- bzw. NMOS-Transistors sowie  $U_{t,i}$  die Schwellensspannung des Transistors i=3,5,6,8. Weil die Transistoren M3 und M8 sowie M5 und M6 jeweils die gleiche Geometrie W/L bzw. die gleichen Verstärkungsfaktoren  $\beta_n$  und  $\beta_p$  sowie daraus folgend gleiche Schwellenspannungen haben, ergibt sich unter Vernachlässigung der Prozeßschwankungen ( $\beta_n = \text{const.}$ ,  $\beta_p = \text{const.}$  und  $\Delta W = 0$ ,  $\Delta L = 0$  sowie  $U_{t,5} = U_{t,6}$  und  $U_{t,3} = U_{t,8}$ ) eine Ausgangsspannung

$$U_{aus} = U_{pix} = U_{ref} - U_{int} = U_{ref} - \frac{S A_D E T_{int}}{C_D + C_S}.$$

(5.4)

Für die Berechnung des FPN dieser Schaltung wird der Einfluß der Prozeßschwankungen berücksichtigt, indem die Schwankungen der erwähnten Größen durch ihre Varianzen beschrieben werden [67]. Zusätzlich wird angenommen, daß die Mittelwerte der Schwellenspannungen von gleich groß gewählten NMOS- und PMOS-Transistoren gleich sind. Ebenso sind die Mittelwerte der Geometriegrößen bzw. Verstärkungsfaktoren von gleich groß gewählten Transistoren identisch

$$\overline{U_{t,3}} = \overline{U_{t,8}}, \quad \frac{\overline{W_3}}{\overline{L_3}} = \frac{\overline{W_8}}{\overline{L_8}} \quad \text{und} \quad \overline{\beta_3} = \overline{\beta_8} = \overline{\beta_n}

\overline{U_{t,5}} = \overline{U_{t,6}} \quad \frac{\overline{W_5}}{\overline{L_5}} = \frac{\overline{W_6}}{\overline{L_6}}, \quad \text{und} \quad \overline{\beta_5} = \overline{\beta_6} = \overline{\beta_p}.$$

(5.5)

Wird noch schließlich der Einfluß der örtlichen Schwankungen des Dunkelstroms  $I_{dark}$  berücksichtigt, muß die Spannung  $U_{int}$  in Gleichung (5.3) wie folgt erweitert werden:

$$U'_{int} = U_{int} + U_{dark} = \frac{S A_D E T_{int}}{C_D + C_S} + \frac{I_{dark} T_{int}}{C_D + C_S}.$$

(5.6)

Wenn für die Varianz der Ausgangsspannung, die sich aus den Varianzen mehrerer unkorrelierter Variablen zusammensetzt, gemäß [89]

$$\sigma_{u_{aus}(x_i)}^2 \approx \sum_{i=1}^n \left( \frac{\partial u_{aus}(x_i)}{\partial x_i} \right)^2 \sigma_{x_i}^2 \bigg|_{\overline{x_1}, \overline{x_2}, \dots \overline{x_n}}$$

(5.7)

geschrieben werden kann, ergibt sich aus den Gleichungen (5.3), (5.6) und (5.7) die Varianz der Ausgangspannung zu

$$\sigma_{u,aus}^{2} = \left(\frac{U_{ref} - \overline{U_{int}} - \overline{U_{t,2}}}{2}\right)^{2} \sum_{\substack{i=3\\i\neq4,7}}^{8} \left(\frac{\sigma_{L,i}^{2}}{\overline{L_{i}}^{2}} + \frac{\sigma_{W,i}^{2}}{\overline{W_{i}}^{2}} + \frac{\sigma_{\beta,i}^{2}}{\overline{\beta_{i}}^{2}}\right) + \left(\frac{\overline{W_{6}} \overline{L_{8}} \overline{\beta_{p}}}{\overline{L_{6}} \overline{W_{8}} \overline{\beta_{n}}}\right) \sigma_{u,t,p}^{2}$$

$$+ 2 \sigma_{u,t,n}^{2} + \left(\frac{T_{int}}{C_{D} + C_{S}}\right)^{2} \sigma_{dark}^{2} + \left(\overline{U_{int}}^{2} + \overline{U_{dark}}^{2}\right) \left[\frac{\sigma_{CD}^{2} + \sigma_{C_{S}}^{2}}{(C_{D} + C_{S})^{2}}\right]. \tag{5.8}$$

Selbst wenn der Einfluß der Prozeßschwankungen der Kondensatoren im Pixel aufgrund ihrer Größen vernachlässigt wird ( $\sigma_{C_S}^2 \approx 0$  und  $\sigma_{C_D}^2 \approx 0$ ) ist es offensichtlich, daß das FPN nicht nur eine signalunabhängige (additive) Komponente, sondern auch eine signalabhängige (multiplikative) Komponente aufweist. Das bedeutet, daß das FPN von der externen Beleuchtung bzw. von der daraus resultierenden integrierten Spannung im Pixel  $U_{int}$  abhängig ist. Aus diesem Grund eignet sich bei einem Stromausleseverfahren keine Implementierung einer korrelierten Doppelabtastung, die in der Lage ist, nur signalunabhängige (additive) und korrelierte Rauschanteile zu unterdrücken. Deswegen hat eine Realisierung dieses Verfahrens in [88] keine umfassende Unterdrückung des Orts-Rauschens erzielt.

#### 5.1.4 Rauschverhalten

Für die Analyse des Rauschverhaltens der in Abbildung 5.1 vorgestellten Schaltung wird für das Rauschen im Pixel auf die im vierten Kapitel vorgestellten Ergebnisse über das kTC-, das Photonen- und das Dunkelstromrauschen zurückgegriffen. Für den Rest der Schaltung inklusive der Ausgangsstruktur des Pixels und der präsentierten Stromauslese-Schaltung werden die Beiträge des thermischen und des 1/f-Rauschens der einzelnen Transistoren berücksichtigt und ihre ausgangsseitige Rauschleistung berechnet. Anschließend werden die einzelnen Beiträge aufgrund der gegenseitigen Unabhängigkeit ihrer Rauschquellen für die gesamte Rauschleistung am Ausgang aufaddiert.

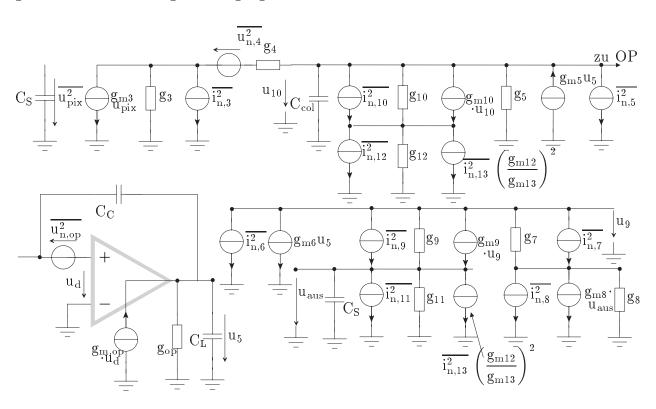

Abbildung 5.2: Das Rauschersatzschaltbild zur Stromauslese-Schaltung.

Ein Rauschersatzschaltbild der zu untersuchenden Schaltung ist in Abbildung 5.2 gezeigt. Der Rauscheinfluß der als Schalter funktionierenden Transistoren M4 und M7 ist gemäß Gleichung (4.45) mit ihren ohmschen Leitwerten  $g_4$  und  $g_7$  bzw. mit den zugehörigen Rauschleistungsdichten der Spannung  $\overline{u_{n,4}^2}$  und des Stroms  $\overline{i_{n,7}^2}$  modelliert. Da die Innenwiderstände der geschlossenen Schalter sehr klein sind, kann der Einfluß ihres thermischen Rauschens in der gesamten Rauschbilanz vernachlässigt werden. Alle anderen im Sättigungsbereich arbeitenden Transistoren sind mit den vollständigen Rauschersatzschaltbildern inklusive der durch die Rauschleistungsdichte des Stromes oder der Spannung beschriebenen Rauschquellen dargestellt. Während das Rauschen der Stromquellentransistoren M11 und M12 mit

den dazugehörigen Rauschleistungsdichten  $(\overline{i_{n,11}^2} \text{ und } \overline{i_{n,12}^2})$  berücksichtigt ist, wird der Rauscheinfluß der Stromquelle  $I_{ref}$  und des Transistors M13 an den Gates von M11 und M12 vernachlässigt. Die von der Stromquelle  $I_{ref}$  und dem Transistors M13 an den Gates von M11 und M12 stammendn korrelierten Rauschanteile, nämlich  $[\overline{i_{n,ref}^2} + \overline{i_{n,13}^2}] (g_{m12}/g_{m13})^2$ werden sich am Ausgang der Schaltung aufheben. Der Einfluß des einpoligen Operationsverstärkers ist mit seiner Steilheit  $g_{m,op}$ , dem Ausgangsleitwert  $g_{ds,op}$  und der zugehörigen Rauschleistung  $\overline{u_{n,op}^2}$  dargestellt. Während für den Operationsverstärker trotz beschriebener Gleichtaktregelung am Knoten S einen Einfluß auf das gesamte Ausgangsrauschen gezeigt werden kann, übt der Operationsverstärker dagegen keinen Einfluß auf die Übertragungsfunktion der anderen Rauschquellen am Ausgang aus. Obwohl die Transistoren M9 und M10 als Gate-Schaltungen eingesetzt sind, wird nur der Rauscheinfluß von M9 am Ausgang vernachlässigt werden [90], während der Rauscheinfluß von M10 aufgrund einer anderen Ubertragungsfunktion zum Ausgang weiter berücksichtigt wird. Der Rauscheinfluß aller anderen in Sättigung arbeitenden Transistoren (M3, M5, M6 und M8) ist durch deren vollständigen Rauschmodelle (siehe Kapitel 4.4.1) mit den zugehörigen Rauschleistungsdichten des thermischen und des 1/f-Rauschens dargestellt, so daß für alle für das Rauschen relevanten Transistoren folgendes gilt:

$$S_{i,3,5,6,8,10}(f) = \frac{8}{3} k T g_{m3,m5,m6,m8,m10} + \frac{k_f}{C'_{ox} W_{3,5,6,8,10} L_{3,5,6,8,10} f} g_{m3,m5,m6,m8,m10}^2,$$

$$S_{i,11,12}(f) = \frac{8}{3} k T g_{m11,m12,m13} + \frac{k_f}{C'_{ox} W_{11,12} L_{11,12} f} g_{m11,m12}^2,$$

$$S_{u,op}(f) = \frac{16}{3} k T \frac{1}{g_{m,op}} + \frac{2 k_f}{C'_{ox} W_{op} L_{op} f},$$

$$(5.9)$$

wobei  $W_j$ ,  $L_j$  Kanalbreiten, Kanallängen und  $g_{mj}$  Steilheit des Transistors j (j=3, 5, 6, 8, 10, 11, 12) bzw.  $W_{op}$ ,  $L_{op}$  und  $g_{m,op}$  als Kanalbreite, Länge und Steilheit des Eingangstransistors des Operationsverstärkers bezeichnen.

Um das dargestellte Rauschersatzschaltbild aus Abbildung 5.2 weiter zu vereinfachen, werden zu den beschriebenen Überlegungen für jeden Transistor und den Operationsverstärker die Ausgangsleitwerte  $g = g_{ds}$  gegenüber einer ausreichend hohen Steilheit  $(g_m \gg g)$  vernachlässigt. Deswegen weden die Ausgangsleitwerte  $g_5$ ,  $g_6$ ,  $g_8$  und  $g_{op}$  aus den weiteren Betrachtungen ausgenommen. Betrachtet man die Gate-Schaltung M10 mit ihrer Last M12, kann ihr äquivalenter Eingangsleitwert gemäß [90] so zusammengefaßt werden, daß unter der Annahme  $g_{m10} \gg g_{10}$  (und  $g_{10} \approx g_{12}$ ) für die weiteren Berechnungen nur ein vereinfachter Wert, d.h. die Steilheit  $g_{m10}$  berücksichtigt wird. Da schließlich eine Rauschanalyse vom kTC-, Photonen- und Dunkelstromrauschen im Pixel vorher schon separat betrachtet wurde, kann die Rauschspannung im Pixel  $\overline{u}_{pix}^2$  (am Kondensator  $C_S$ ) und daher die Stromquelle  $g_{m3}u_{pix}$  zu Null gesetzt werden. All diesen beschriebenen Überlegungen zur Folge vereinfacht

sich das Rauschersatzschaltbild wie in Abbildung 5.3 gezeigt.

Abbildung 5.3: Das vereinfachte Rauschersatzschaltbild zur Stromauslese-Schaltung.

Die Berechnung der ausgangsseitigen Rauschleistung erfolgt, indem zunächst die Übertragungsfunktion  $H_{v/i,j}(s)$  der einzelnen Rauschquellen bis zum Ausgang der Schaltung berechnet wird. Anschließend wird unter Berücksichtigung der Spektralleistungsdichte  $S_{n,j}$  der zugehörigen Rauschquelle und des Betragsquadrates der Übertragungsfunktion  $\left|H_{v/i,j}(s)\right|^2$  die ausgangsseitige Rauschleistung nach der Integration des Produktes der zwei erwähnten Größen über den gesamten Frequenzbereich gemäß der folgenden Gleichung ermittelt:

$$\overline{u_{n,j}^2} = \int_0^\infty |H_{i,j}(s)|^2 |S_{n,j}(f)| df.$$

(5.10)

Um die Übertragungsfunktion der Rauschanteile, die von den Transistoren M3, M5 und M10 stammen, zu bestimmen, werden die aufgrund der bei einem CMOS-Bildsensor hohen Spaltenleitungskapazität sowie der für die Geschwindigkeit der Schaltung relevanten Verhältnisse der Kapazitäten und Steilheiten berücksichtigt. So ergibt sich das Kapazitätsverhältnis  $C_{col} \gg C_C$ , wobei  $C_{col}$  die parasitäre Leitungkapazität und  $C_C$  die Kompensationskapazität des Operationsverstärkers darstellen. Da die Transistoren M5 und M6 gleich groß sein müssen, besitzen sie gleich große Steilheiten  $g_m = g_{m5} = g_{m6}$ . Der Einfachheit halber wird zudem angenommen, daß die Steilheit des Transistors M10 diesen Steilheiten ebenso  $g_{m10} = g_m$  gleicht. Wenn neben diesen Überlegungen zusätzlich die Beziehung  $g_{m,op}/C_L \gg g_{m5}/C_{col}$

gilt (die Polstelle des Operationsverstärkers ist viel größer als diejenige, die durch den Tiefpaß bestimmt ist, der sich am Knoten der Spaltenleitung bildet), ergibt sich die gesuchte Übertragungsfunktion zu

$$H_{3,5,10}(s) = \frac{g_{m6}}{g_{m8}} \frac{1}{\left(1 + s \frac{C_S}{g_{m8}}\right)} \cdot \frac{1}{g_{m5}} \frac{1 + s \frac{C_C}{g_{m,op}}}{\left(1 + s \frac{C_L}{g_{m,op}}\right) \left(1 + s \frac{C_{col}}{g_m}\right)}.$$

(5.11)

Betrachtet man die Null- und Polstellen der gegebenen Übertragungsfunktion, läßt sie sich aufgrund der gegebenen Beziehungen über die Polstellen  $(g_{m,op}/C_L \gg g_m/C_{col})$  sowie über die Steilheit der Transistoren weiter vereinfachen. Da zudem die Polstelle  $g_{m8}/C_S$  und die Nullstelle  $g_{m,op}/C_C$  viel größer als die zuvor erwähnte Polstelle  $g_m/C_{col}$  sind<sup>1</sup>, ergibt sich daraus eine vereinfachte Übertragungsfunktion zu

$$H_{3,5,10}(s) = \frac{1}{g_{m8}} \frac{1}{1 + s \frac{C_{col}}{g_m}}.$$

(5.12)

Wenn diese Übertragungsfunktion für die ausgangsseitigen Rauschleistungen der Transistoren M3, M5 und M10 gemäß der Gleichung (5.10) mit zugehörigen Rauschleistungsdichten des weißen Rauschens berücksichtigt wird, errechnet sich die Rauschleistung des weißen Rauschens am Ausgang zu

$$\overline{u_{n,aus,3,5,10,weiß}^{2}} = \underbrace{\frac{2}{3} \frac{kT}{C_{col}} \left(\frac{g_{m}}{g_{m8}}\right)}_{M3} + \underbrace{\frac{2}{3} \frac{kT}{C_{col}} \left(\frac{g_{m}}{g_{m8}}\right)^{2}}_{M5} + \underbrace{\frac{2}{3} \frac{kT}{C_{col}} \left(\frac{g_{m}}{g_{m8}}\right)^{2}}_{M10} \tag{5.13}$$

wobei bei den gegebenen Beziehungen der Steilheiten aus Symmetriegründen ebenso  $g_{m3} = g_{m8}$  gilt. Wird das Betragquadrat der Übertragungsfunktion mit der Rauschleistungsdichte des 1/f-Rauschens der Transistoren M3, M5 und M10 multipliziert und über den Frequenzbereich integriert, erhält man gemäß [91] nach kurzer Berechnung die zugehörige ausgangsseitige Rauschleistung des 1/f-Rauschens wie folgt:

$$\frac{\overline{u_{n,aus,3,5,10,1/f}^{2}} = \frac{k_{f}}{C_{ox}'} \left[ \underbrace{\frac{1}{W_{3} L_{3}}}_{M3} + \underbrace{\frac{1}{W_{5} L_{5}} \left(\frac{g_{m}}{g_{m8}}\right)^{2}}_{M5} + \underbrace{\frac{1}{W_{10} L_{10}} \left(\frac{g_{m}}{g_{m8}}\right)^{2}}_{M10} \right] \ln \left(\frac{g_{m}}{C_{col} \omega_{0}}\right). (5.14)$$

<sup>&</sup>lt;sup>1</sup>Kapazitäten  $C_S$  und  $C_C$  sind mindestens eine Größenordnung kleiner als  $C_{col}$ ,  $C_L$  und zudem ebenso gilt  $g_{m,op} \gg g_{m8}$ .

Für den Rauscheinfluß des Stromquellentransistors M12 kann aufgrund des geringfügig modifizierten Rauschersatzschaltbildes in Abbildung 5.3 einfach gezeigt werden, daß sich gleiche Übertragungsfunktion wie in Gleichung (5.12) ergibt. Daher ergibt sich nach der Integration des Betragsquadrates der Übertragungsfunktion mit den zugehörigen Rauschleistungsdichten des weißen und des 1/f-Rauschens für den Transistor M12 folgende ausgangsseitige Rauschleistung

$$\overline{u_{n,aus,12}^2} = \frac{2}{3} \frac{k T}{C_{col}} \frac{g_m g_{m12}}{g_{m8}^2} + \frac{k_f}{C'_{ox}} \frac{1}{W_{12} L_{12}} \left(\frac{g_{m12}}{g_{m8}}\right)^2 \ln\left(\frac{g_m}{C_{col} \omega_0}\right).$$

(5.15)

Für die Ermittlung des Rauschbeitrags des Operationsverstärkers zu der gesamten ausgangsseiten Rauschleistung wird die Übertragungsfunktion von der Rauschquelle  $\overline{u_{n,op}^2}$ , mit der der Operationsverstärker modelliert ist, bis zum Ausgang der Ausleseschaltung berechnet. Unter gleichen Annahmen wie für die Übertragungsfunktion der zuvor ermittelten Rauschquellen ergibt sich unter Berücksichtigung der relevanten Terme

$$H_{op}(s) = \frac{1}{g_{m8}} \frac{1}{1 + s \frac{C_L}{g_{m,op}}}.$$

(5.16)

Wenn das Betragsquadrat dieser Übertragungsfunktion zusammen mit ihren zugehörigen Rauschleistungsdichten des weißen und des 1/f-Rauschens wiederum in Gleichung (5.10) eingesetzt wird, errechnet sich die ausgangsseitige Rauschleistung des Operationsverstärkers inklusive des weißen und des 1/f-Rauschens als

$$\overline{u_{n,aus,op}^2} = \frac{4}{3} \frac{k T}{C_L} \left(\frac{g_{m,op}}{g_{m8}}\right)^2 + \frac{2 k_f}{C'_{ox} W_{op} L_{op}} \left(\frac{g_{m,op}}{g_{m8}}\right)^2 \ln \frac{g_{m,op}}{C_L \omega_0}.$$

(5.17)

Für die Rauschbeiträge der Transistoren M6, M8 und M11 kann zum Ausgang der Schaltung folgende Übertragungsfunktion ermittelt werden

$$H_{6,8,11}(s) = \frac{1}{g_{m8}} \frac{1}{\left(1 + s \frac{C_S}{g_{m8}}\right)},\tag{5.18}$$

deren Betrag zum Quadrat nach der Integration mit den (5.10) folgende ausgangsseitige Rauschleistung ergibt:

$$\overline{u_{n,aus,6,8,11}^{2}} = \underbrace{\frac{2}{3} \frac{k T}{C_{S}} \left(\frac{g_{m}}{g_{m8}}\right)}_{M6} + \underbrace{\frac{2}{3} \frac{k T}{C_{S}}}_{M8} + \underbrace{\frac{2}{3} \frac{k T}{C_{S}} \left(\frac{g_{m11}}{g_{m8}}\right)}_{M11} + \underbrace{\frac{k_{f}}{C'_{ox}} \left[\underbrace{\frac{1}{W_{6} L_{6}} \left(\frac{g_{m}}{g_{m8}}\right)^{2}}_{M6} + \underbrace{\frac{1}{W_{8} L_{8}}}_{M8} + \underbrace{\frac{1}{W_{11} L_{11}} \left(\frac{g_{m11}}{g_{m8}}\right)^{2}}_{M11}\right] \ln \left(\frac{g_{m8}}{C_{S} \omega_{0}}\right). \quad (5.19)$$

Unter Berücksichtigung des Photonen-, Dunkelstrom- und kTC-Rauschens im Pixel aus den Gleichungen (4.24), (4.25) und (4.29) sowie aller ausgangsseitigen Rauschleistungsbeiträge aus den Gleichungen (5.13), (5.14), (5.15), (5.17) und (5.19) ergibt sich unter der Annahme der gegenseitigen Unabhängigkeit aller Rauschquellen eine gesamte ausgangsseitige Rauschleistung als Summe aller diesen Rauschterme zusammengefaßt zu

$$\frac{1}{u_{n,aus}^{2}} = \frac{q\left(U_{int} + U_{dark}\right)}{C_{D} + C_{S}} + kT\left(\frac{1}{C_{D}/2 + C_{S}} + \frac{C_{D}}{C_{S}} \frac{1}{C_{D} + C_{S}}\right) + \frac{2}{3} \frac{kT}{C_{col}} \left[\frac{g_{m}}{g_{m8}} + 2\left(\frac{g_{m}}{g_{m8}}\right)^{2} + \frac{g_{m}g_{m12}}{g_{m8}^{2}}\right] + \frac{k_{f}}{C_{ox}'} \left[\frac{1}{W_{3}L_{3}} + \left(\frac{1}{W_{5}L_{5}} + \frac{1}{W_{10}L_{10}}\right)\left(\frac{g_{m}}{g_{m8}}\right)^{2} + \frac{1}{W_{12}L_{12}}\left(\frac{g_{m12}}{g_{m8}}\right)^{2}\right] \ln 10 ND_{e,0} + \frac{4}{3} \frac{kT}{C_{L}} \left(\frac{g_{m,op}}{g_{m8}}\right)^{2} + \frac{k_{f}}{C_{ox}'} \frac{1}{W_{op}L_{op}}\left(\frac{g_{m,op}}{g_{m3}}\right)^{2} \ln (10) ND_{e,1} + \frac{2}{3} \frac{kT}{C_{S}} \left[1 + \left(\frac{g_{m}}{g_{m8}}\right)^{2} + \frac{g_{m11}}{g_{m8}}\right] + \frac{k_{f}}{C_{ox}'} \left[\frac{1}{W_{6}L_{6}}\left(\frac{g_{m}}{g_{m8}}\right)^{2} + \frac{1}{W_{8}L_{8}} + \frac{1}{W_{12}L_{12}}\left(\frac{g_{m12}}{g_{m8}}\right)^{2}\right] \ln (10) ND_{e,2}, \tag{5.20}$$

wobei  $ND_{e,0} = \ln(g_m/C_{col}\,\omega_0), ND_{e,1} = \ln(g_{m,op}/C_L\,\omega_0)$  und  $ND_{e,2} = \ln(g_{m8}/C_S\,\omega_0)$  Dekadenzahlen darstellen, über die sich das 1/f-Rauschen ausstreckt. Um eine zuverlässige Signalspeicherung während der Auslese, geringe Ladungsinjektion während der Schaltvorgänge, einen günstigen Füll-Faktor, usw. zu gewährleisten, werden die Pixelkapazitäten, wie vorher vorgeschlagen, gleichgesetzt  $(C_D = C_S)$ . Um dabei möglichst kleine Pixeldimensionen zu erfüllen, soll Kapazität  $C_S$  als parasitäre Kapazität am Gate von Transistor M3 (Transkonduktanzverstärker im Pixel) realisiert werden. Um die Größes des Transistors M3 zu bestimmen, muß bei der Auswahl seiner Geometrie ein Kompromiß zwischen den zuvor genannten Anforderungen ( $W_3 L_3$  groß) und dem hohen Füll-Faktor ( $W_3 L_3$  klein) gefunden werden. Weil zudem die Steilheit dieses Transistors M3 unter dem Aspekt der Verlustleistung nicht zu groß gewählt werden darf, ergibt sich bei einer hohen angestrebten Geschwindigkeit der Stromausleseschaltung die Beziehung  $g_m \gg g_{m8}$ . Deswegen muß das 1/f-Rauschen trotz gegebener Geometrieverhältnisse  $(W_5 L_5, W_{10} L_{10} \gg W_3 L_3)$  sowie  $W_{11}$   $L_{11}$ ,  $\gg W_3$   $L_3$ ) bei dieser Schaltung in der gesamten Rauschbilanz einkalkuliert werden. Dagegen können nur die Rauschanteile, die durch den Kapazitäten  $C_{col}$  und  $C_L$  bandbegrenzt sind, gegenüber denjenigen vernachlässigt werden, die durch  $C_S$  bandbegrenzt sind. Folgend diesen Überlegungen ergibt sich die gesamte ausgangsseitige Rauschleistung zu

$$\overline{u_{n,aus}^2} = \frac{q}{2C_D} \left[ U_{int} + \left( \frac{11}{6} + \frac{2}{3} \left( \frac{g_m}{g_{m8}} \right)^2 \right) U_T \right] + \overline{u_{n,aus,1/f}^2},$$

(5.21)

wobei  $U_T=k\,T/q$  die Temperaturspannung und  $\overline{u_{n,aus,1/f}^2}$  die Rauschleistung des 1/f-Rauschens darstellen. Aus Gleichung (5.21) ist ersichtlich, daß der Einfluß des Dunkelstromrauschens vernachlässigt ist. Bei der vorgegebenen Annahme, daß Füll-Faktor 40 % beträgt, ergibt sich für eine angenommene Pixelgröße von  $25\times25\,\mu\mathrm{m}^2$  bei einem gemessenen Dunkelstrom von  $20\,\mathrm{aA}/\mu\mathrm{m}^2$  in  $1\,\mu\mathrm{m}$  CMOS-Prozeß folgende Überlegung: bei einer Photodiode mit der Fläche von  $250\,\mu\mathrm{m}^2$ und einer Kapazität von  $C_D=50$  fF erzeugt der Dunkelstrom bei einer Integrationszeit von  $150\,\mu\mathrm{s}$  nur  $\overline{N}=I_{dark}\,A_D\,T_{int}=5\,e^-$  Rauschelektronen. Dagegen würde das kTC-Rauschen im Pixel gemäß der Formel (4.29)  $90\,e^-$  Rauschelektronen auslösen, was deutlich größer als der Anteil des Dunkelstromrauschens ist. Wenn zu diesen Überlegungen das 1/f-Rauschen vernachlässigt wird, können die für den Bildsensor relevanten Größen wie Signal-Rausch-Verhältnis und Dynamikbereich abgeschätzt werden. Da das gesamte Rauschen am Ausgang bei Bildsensoren durch das Photonenrauschen ohnehin dominiert wird, ergibt sich das Signal-Rausch-Verhältnis dieser Schaltung, das sowohl durch das Photonen- als auch durch das höhere kTC- Rauschen beeinflußt wird, zu

$$SNR_{dB,max} = 10 \log \frac{C_D U_{int}^2}{q \left[ U_{int} + \left( \frac{11}{6} + \frac{2}{3} \frac{g_m^2}{g_{m8}^2} \right) U_T \right]}.$$

(5.22)

Bei einer Diodenkapazität  $C_D=50\,\mathrm{fF}$  und einem Signalhub von 2.5 V errechnet sich für das Signal-Rausch-Verhältnis ein Wert von 58 dB. Der Dynamikbereich dieser Schaltung resultiert unter alleiniger Berücksichtigung des kTC-Rauschens als das Grundrauschen der Schaltung zu

$$DR_{dB} = 10 \log \frac{C_D U_{int}^2}{\left(\frac{11}{6} + \frac{2}{3} \frac{g_m^2}{g_{m8}^2}\right) q U_T}.$$

(5.23)

Für die gleiche Diodenkapazität  $C_D=50\,\mathrm{fF}$  sowie den gleichen Spannungshub von 2.5 V beziffert sich der Dynamikbereich zu 63 dB.

Weder beim Signal-Rausch-Verhältnis noch beim Dynamikbereich wurde der Einfluß von FPN berücksichtigt. Dies folgt aus der Tatsache, daß dieses örtliche Rauschen mit Hilfe softwaretechnischer Maßnahmen erfolgreich beseitigt werden kann.

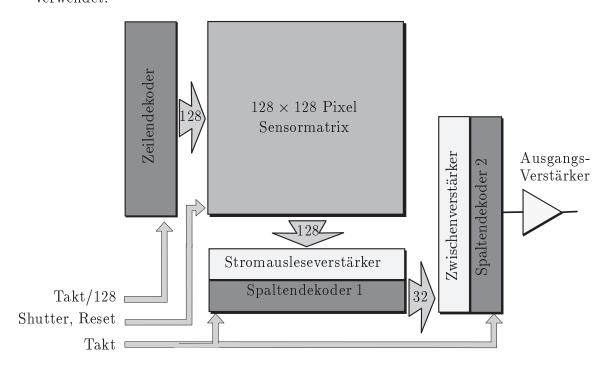

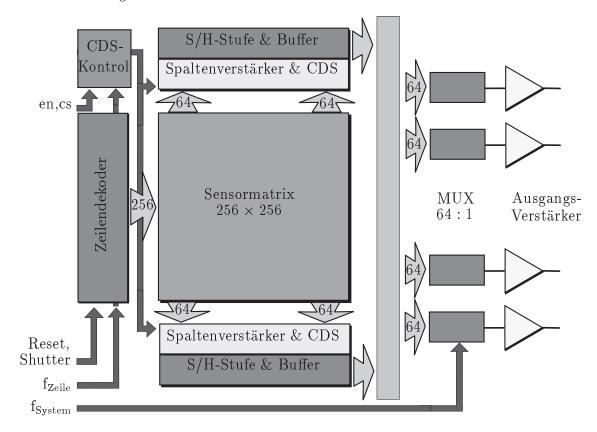

#### 5.1.5 Sensorarchitektur

Der gesamte Aufbau des realisierten CMOS-Bildsensors ist in Abbildung 5.4 gezeigt. Die Schaltung verfügt nicht über eine in CMOS-Technik realisierbare wahlfreie Adressierung der Pixel. Stattdessen "scannen" die Schieberegister in einem sequentiellen Vorgang die gesamte photoempfindliche Matrix (progressiver Scan-Betrieb). Für eine zeilenweise Abarbeitung der Pixelinformation wird ein Zeilenschieberegister und für eine pixelweise Auslese der akquirierten Bildinformation aus der angesprochenen Zeile werden zwei Spaltenschieberegister verwendet.

Abbildung 5.4: Architektur des CMOS-Bildsensors mit Stromausleseprinzip.

Wenn eine Zeile angewählt ist, werden mittels einer Bank der vorgestellten Stromausleseverstärker die akquirierten Signalwerte parallel aus der Matrix ausgelesen. Die präsentierte baumförmige Konfiguration mit zwei Spaltenschieberegistern und zwei Verstärkerstufen ermöglicht eine günstige Verteilung der Ausgangslasten in der gesamten Ausleseelektronik. Anstatt wie in einer Standardkonstellation (siehe Abbildung 4.1) während der Auslese eines Pixelwertes 127 geöffnete Schalter innerhalb eines 128 : 1-Multiplexers und einen Ausgangsverstärker höherer Eingangsimpedanz zu treiben, müssen in dieser Konstellation die Stromausleseverstärker nur drei geöffnete Schalter und einen mit geringer Eingangsimpedanz behafteten Zwischenverstärker treiben. Die Zwischenverstärker sind auf einer vierfachen Pixelbreite im Layout plaziert und müssen ihrerseits 31 geöffnete Schalter des 32 : 1-Multiplexers und den Ausgangsverstärker treiben. Die beschriebene Struktur der Ausleseelektronik ermöglicht bei einem hohen Pixeltakt von 22 MHz den Einsatz von leistungsär-

meren und insgesamt weniger Platz bedürftigen analogen Verstärkern.

## 5.1.6 Meßergebnisse und Chipdaten des $128 \times 128$ Bildsensors

Der hier beschriebene CMOS-Bildsensor wurde im Rahmen des High-Frame-Rate Kamera Projekts mit einer Auflösung von 128 × 128 Pixeln realisiert [92, 93]. Die angestrebte Zielsetzung als ein Nachweis für den Einsatz der CMOS-Schaltungstechnik in der Hochgeschwindigkeits-Bildsensorik wurde erfolgreich erreicht. Die erzielten Ergebnisse bestätigen die Fähigkeit der CMOS-Technik nicht nur für diese angestrebte Anwendung, sondern darüber hinaus eröffnen die zusätzlichen Möglichkeiten der CMOS-Bildsensorik für den Einsatz im Maschinellen Sehen und in der optischen Meßtechnik.

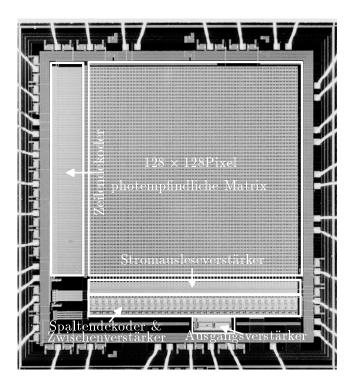

Das Chipphoto des in einer zur Verfügung stehenden 1  $\mu$ m Standard-CMOS-Technologie realisierten Bildsensors ist in Abbildung 5.5 gezeigt. In dem Chipphoto finden sich einzelne Baugruppen wieder, die bei der Vorstellung der Sensorarchitektur beschrieben worden sind.

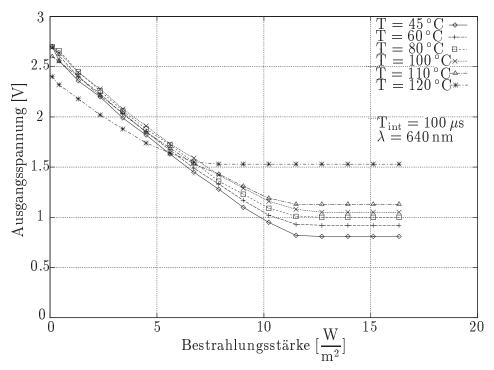

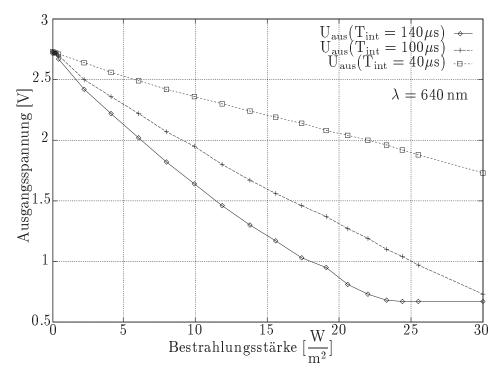

Die gemessene Übertragungscharakteristik, die in Abbildung 5.6 gezeigt ist, präsentiert das Sensorverhalten bei der Integrationszeit von  $100~\mu s$  unter verschiedenen Temperaturen. Die Responsivität bei  $T=40~^{\circ}C$  beträgt  $1600~V/J/m^2$ . Mit höheren Temperaturen werden die Kennlinien "flacher" d.h. die Responsivität sinkt. Außerdem wird der effektive Signalhub geringer, so daß mit erhöhtem Rauschen das Signal-Rausch-Verhältnis und der Dynamikbereich kleiner werden. Bis auf  $T=110~^{\circ}C$  ändert sich die Übertragungscharakteristik geringfügig. Der Einfluß der nichtlinearen Detektorkapazität im Pixel  $C_D$  (aufgrund der C-V-Diodenkennline) auf die Übertragungscharakteristik hat sich als gering erwiesen, was durch eine gute Linearität in gleicher Abbildung festzustellen ist.

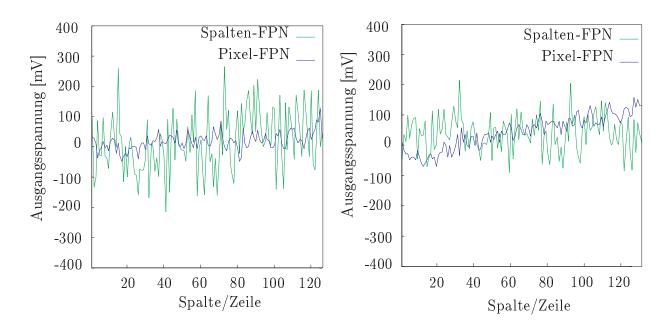

Die Problematik des FPNs bei diesem Sensor ist in Abbildung 5.7 dokumentiert. Das örtliche Rauschen ist dabei für zwei unterschiedliche Beleuchtungsverhältnisse, nämlich für eine homogen helle und eine homogen dunkle Szene, gemessen worden. In jedem einzelnen Fall unterscheidet sich das FPN innerhalb einer Spalte (Pixel-FPN) und das FPN zwischen den Spalten (Spalten-FPN). Wie aus Gleichung (5.5) folgt, ist das FPN signal- bzw. beleuchtungsabhängig, wobei ein höheres FPN einem höheren Wert des integrierten Signals, d.h. einer höheren Beleuchtung entspricht. Ein höheres Spalten- als Pixel-FPN war nach der erwähnten Gleichung aufgrund einer größeren Anzahl der zu matchenden Transistoren im Stromausleseverstärker als im Pixel zu erwarten. Ein über die Beleuchtung gemittelter Wert des FPNs ist für diesen Sensor 130 mV oder 5.5 % des gesamten Spannungshubes.

Das gemessene SNR von 54 dB ist geringfügig kleiner als in der Berechnung, was durch eine Vernachlässigung des 1/f-Rauschens bei seiner Berechnung zustande kommt. Die Folge der Vernachlässigung des 1/f-Rauschens ist noch ausgeprägter bei einem vergleichsweise deutlich geringeren Dynamikbereich, dessen Wert von 58 dB gemessen wurde.

Abbildung 5.5: Das Chipphoto des  $128 \times 128$  Pixel großen CMOS-Bildsensors.

Abbildung 5.6: Die gemessene Übertragungscharakteristik des  $128 \times 128$  Bildsensors.

Abbildung 5.7: Das gemessene örtliche Rauschen des 128 × 128 Bildsensors einer homogen hellen Szene (links) und einer homogen dunklen Szene (rechts).

| CMOS-Bildsensor für Hochgeschwindigkeitsanwendungen |                                                          |

|-----------------------------------------------------|----------------------------------------------------------|

| Auflösung                                           | $128 \times 128$ Pixel                                   |

| Pixelgröße                                          | $27.6 \ \mu m \times 27.6 \ \mu m$                       |

| Füll-Faktor                                         | 42 %                                                     |

| Chipfläche                                          | $32  mm^2$ in $1 \mu m$ -CMOS-Prozeß                     |

| Integrationszeit                                    | $> 150  \mu s$ bei den Bildraten $50  -  1000  Bilder/s$ |

|                                                     | $1-150\mu s$ im Standard-Betrieb                         |

|                                                     | > 30  ns im gepulsten Betrieb                            |

| Bildrate                                            | $1030 \ Bilder/s$ bei $100 \ \mu s$ Integrationszeit     |

| Pixelrate                                           | 22MHz                                                    |

| Maximales SNR                                       | 54 dB                                                    |

| DR                                                  | 58 dB                                                    |

| Blooming                                            | nicht bemerkbar                                          |

| Smearing, Lag                                       | nicht bemerkbar                                          |

| FPN                                                 | 5.5% des vollen Signalhubes ("full scale", FS)           |

| Verlustleistung                                     | 280mW bei $5V$ Spannungsversorgung                       |

Tabelle 5.1: Technische Daten des  $128 \times 128$  CMOS-Bildsensors für Hochgeschwindigkeits-anwendungen.

Alle diese Werte sind bei einer Rate von 1030 Bilder/s und einer Integrationszeit von 100  $\mu$ s ermittelt worden. Eine bemerkenswerte Einschränkung der Sensorleistung bei der Verlängerung der Integrationszeit, sowie einer damit verknüpften geringeren Bildrate war aufgrund des höheren Dunkelstromrauschens bis hinab zu TV-Bildraten nicht festzustellen. Der Bildsensor funktioniert daher zusätzlich bei allen Bildraten, die zwischen TV-Bildraten und 1000 Bilder/s liegen. Insbesondere interessant ist eine Verkürzung der Integrationszeit unterhalb der erwähnten 100  $\mu$ s. Bis zu 1  $\mu$ s bleiben die Sensoreigenschaften gut erhalten. Dies bezieht sich unter anderem vor allem auf eine Unterdrückung der Smearing- und Blooming-Effekte. Die Anwendung des Bildsensors bei Integrationszeiten im Nanosekunden-Bereich ist in einer Kombination mit einer externen modulierten Beleuchtung ebenso möglich, worauf im fünften Kapitel näher eingegangen wird.

Eine Zusammenfassung aller wichtigen Sensordaten ist in Tabelle 5.1 gegeben. Die angegebenen Daten über SNR, DR, Blooming und Smearing wurden für den Sensorbetrieb bei 1030 Bilder/s und  $100 \mu$ s Integrationszeit gemessen.

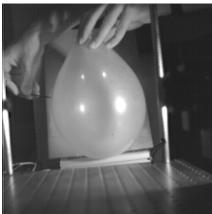

Die Abbildung 5.8 zeigt zwei mit diesem Sensor aufgenommene Bilder bei einer Integrationszeit von  $50~\mu s$  bzw.  $100~\mu s$  und einer Bildrate von 1030~Bilder/s. Die Aufnahmen der mit diesem Sensor akquirierten vollständigen Bildsequenzen der sich schnell abwickelnden Ereignisse werden im nächsten Kapitel über die Anwendungen der schnellen CMOS-Bildsensorik präsentiert.

Abbildung 5.8: Aufnahmen der CMOS-Kamera mit  $128 \times 128$  Pixel bei Integrationszeiten von  $50 \mu s$  bzw.  $100 \mu s$  und einer Bildrate von 1030 Bilder/s.

# 5.1.7 Systemkonzept für die Kamera mit reduzierter Auflösung

Um den CMOS-Bildsensor für Hochgeschwindigkeitsanwendungen funktionsfähig zu machen, ist eine Systemumgebung für seinen Betrieb notwendig. Da der Bildsensor mit Stromauslese über 128×128 Bildelemente verfügt, ist bei einem Pixeltakt von 22 MHz die Datenmenge noch akzeptabel, die zu einem PC-Rechner übertragen, abgespeichert und visualisiert werden soll. Infolgedessen muß ein Kamerasystem keine zusätzlichen Bausteine für eine temporäre

Datenspeicherung im System selbst enthalten. Da der CMOS-Sensor die Signale über die akquirierte Bildinformation in einer analogen Form liefert, ist eine für den Sensor externe, aber im Kamerasystem enthaltene Digitalisierung der Signale notwendig. Außer einer Digitalisierung der analogen Signale liefert das System in einem FPGA-Baustein erzeugte Steuersignale für den Sensor selbst, sowie mittels der zur Verfügung stehenden Bias-Referenznetzwerke die für den Sensorbetrieb notwendigen Biasspannungen. Nachdem die digitalisierten Signale in ein geeignetes Format aufbereitet sind, erfolgt eine Übertragung zum PC-Rechner. Ein solches realisiertes System ist in [93] präsentiert.

Neben dem hardware-technischen Aufbau disponiert das System über einen einfachen Algorithmus zur Aufhebung des örtlichen Rauschens. Zurückgreifend auf die in Gleichung (5.5) beschriebene Natur des FPNs läßt sich daraus schließen, daß der Algorithmus den Fehler des additiven und des multiplikativen Charakters beheben muß. Wenn ein linearer Bildsensor ein Signal  $U_{raw,(i,j)}$  aus jedem beliebigen Pixel (i,j) aus der photoempfindlichen Matrix am Chipausgang (nach der gesamten Ausleseelektronik aus Abbildung 5.4) erzeugt, das von signalunabhängigem FPN (additiver oder Fehler 0-er Ordnung) und dem sigalabhängigen FPN (multiplikativer oder Fehler 1-er Ordnung) beeinträchtigt ist, müssen zwei Korrekturwerte  $G_{(i,j)}$  und  $U_{off,(i,j)}$  errechnet werden, um daraus ein korrigiertes Signal  $U_{korr,(i,j)}$  am Chipausgang für das Pixel (i,j) zu ermitteln

$$U_{korr,(i,j)} = G_{(i,j)} U_{raw,(i,j)} + U_{off,(i,j)}.$$

(5.24)

Um für die Übertragungscharakteristik des gesamten Pixelarrays die Korrekturkoeffizienten zu ermitteln, sind zwei Referenzmessungen mit einer homogen hellen Szene  $(E_{hell})$  und einer homogen dunklen Szene  $(E_{dunk})$  notwendig. Aus diesen Referenzmessungen sind ein Mittelwert der Ausgangsspannung der dunklen  $\overline{U(E_{dunk})}$  bzw. der hellen Szene  $\overline{U(E_{dunk})}$  zu ermitteln. Mit diesen zwei Werten, die eine Soll-Übertragungskennlinie bestimmen, und mit den Ausgangsspannungen jedes Pixels i für eine dunkle  $U_{raw,(i,j)}(E_{dunk})$  und eine helle Szene  $U_{raw,(i,j)}(E_{hell})$  lassen sich die Korrekturkoeffizienten für jedes Pixel (i,j) berechnen zu

$$G_{(i,j)} = \frac{\overline{U(E_{dunk})} - \overline{U(E_{hell})}}{U_{raw,(i,j)}(E_{dunk}) - U_{raw,(i,j)}(E_{hell})}$$

$$U_{off,(i,j)} = \frac{U_{raw,(i,j)}(E_{dunk})\overline{U(E_{hell})} - U_{raw,(i,j)}(E_{hell})\overline{U(E_{dunk})}}{U_{raw,(i,j)}(E_{dunk}) - U_{raw,(i,j)}(E_{hell})}.$$

(5.25)

Der für die FPN-Korrektur vorgestellte Algorithmus funktioniert unabhängig von der Integrationszeit  $T_{int}$ . Da für die Hochgeschwindigkeitskinematographie eine Echtzeitfunktionalität nicht unbedingt erforderlich ist, kann der Algorithmus auch nach der Datenspeicherung, d.h. unabhängig von der Bildrate angewendet werden.

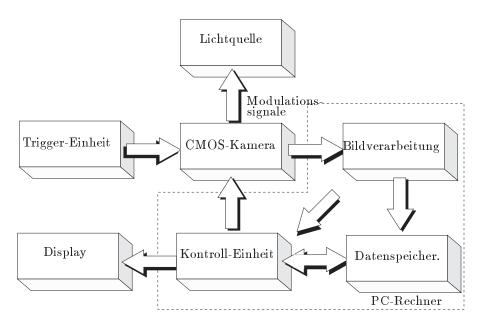

Ein so beschriebenes Kamerasystem mit allen Hardware- und Software-Komponenten inklusive einer benutzerfreundlichen graphischen Oberfläche ist ebenso im Rahmen des High-Frame-Rate Kamera Projekts entwickelt worden. Ein Blockschaltbild dieses Systems ist in Abbildung (5.9) gezeigt. Die Hochgeschwindigkeitskamera liefert digitale Daten im RS-422 Format zum Framegrabber im Rechner, der mittels der gewonnenen Daten aus den zwei Referenzmessungen des beschriebenen Algorithmus eine FPN-Korrektur durchführt. Im Standard-Modus des Kamerasystems wird die aufgenommene Szene bei Videobildwiederholrate auf dem Monitor angezeigt. Im Aufnahme-Modus, der mit einem Triggersignal ausgelöst wird, werden die Bilddaten bei mehr als 1000 Bilder/s akquiriert und von der Kamera in den Speicher vom Rechner transferiert. Das Kamerasystem kann auch Steuersignale zur Modulation einer Lichtquelle (z.B. Laser, LED) liefern. Auf die verschiedenen Anwendungsgebiete des in das Kamerasystem eingebetteten CMOS-Bildsensors über die Standard-Hochgeschwindigkeitsanwendung hinaus wird im sechsten Kapitel näher eingegangen.

Abbildung 5.9: Das Blockschaltbild des entwickelten Kamerasystems mit einem  $128 \times 128$  Pixel großen CMOS-Bildsensor für Hochgeschwindigkeitsanwendungen.

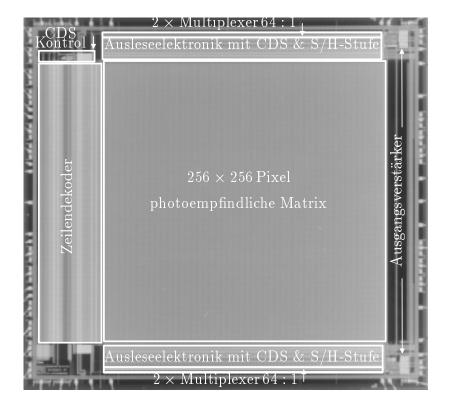

# 5.2 Das schnelle CMOS-Sensorsystem mit On-Chip Bildverbesserung

Die Zielsetzung des zweiten hier vorgestellten CMOS-Bildsensors sieht einen hochwertigen Hochgeschwindigkeits-Bildsensor vor, der bei einer höheren Auflösung die Bildaufnahmen bei Bildraten von mehr als 1000 Bilder/s mit einer On-Chip-Bildverbesserung ermöglicht.

Für eine Realisierung dieses mit  $256 \times 256$  Pixel großen Bildsensors stand wiederum eine  $1~\mu m$  Standard-CMOS-Technologie zur Verfügung. Bei ähnlich angestrebten Spezifikationen wie beim zuerst vorgestellten Bildsensor bezüglich des Signal-Rausch-Verhältnisses und des Dynamikbereichs (SNR = 60~dB und DR > 45~dB) sowie einer Implementierung des elektronischen Shutters soll dieser CMOS-Bildsensor trotz hoher Pixelraten über eine On-Chip Rauschunterdrückung (inklusive zeitliches und örtliches Rauschens) verfügen. Um große Datenmengen bewältigen zu können, die bei einem hohen Pixeltakt aufgrund der höheren Auflösung entstehen, ist eine mehrkanalige Sensorstruktur vorgesehen.

#### 5.2.1 Motivation

Obwohl der zuerst vorgestellte Bildsensor einen großen Fortschritt bezüglich der Realisierung und des Funktionsbereichs des elektronischen Shutters darstellt und aufgrund der Realisierung in einer Standard-CMOS-Technologie die Kosten erheblich gesenkt hat, kann für eine sehr gute Qualität der aufgenommenen Bilder eine FPN-Reduktion ohne externen Aufwand nicht bewerkstelligt werden. Überdies wäre eine zusätzliche Reduktion des zeitlichen Rauschens in Hinblick auf die relevanten Sensorkenngrößen (Signal-Rausch-Verhältnis, Dynamikbereich, usw.) erwünscht.

Um dies zu verwirklichen, ist bei der Realisierung eines anderen Konzepts für schnelle CMOS-Bildsensoren eine langsamere Spannungsauslese in Kombination mit einem korrelierten Doppelabtastverfahren (CDS) angestrebt worden. Das Spannungsausleseverfahren ist trotz seiner zu dem Stromausleseverfahren vergleichsweise langsameren Auslese der Signale aus den Pixeln gewählt worden, weil es aufgrund seiner Natur nur eine signalunabhängige Komponente des FPNs verursacht. Da sich gleichzeitig mit einem CDS-Verfahren nur signalunabhängige Anteile der örtlichen Schwankungen beheben lassen, eignet sich dieses Verfahren für die Implementierung einer On-Chip FPN-Korrektur. Zusätzlich, wie schon im vierten Kapitel erklärt, reduziert das CDS ebenso vor allem das niederfrequente zeitliche Rauschen der Schaltung. Ein ohnehin durch eine Spannungsauslese bei hohen Bildraten verursachtes kritisches Zeitschema wird durch den Einsatz des CDS-Verfahrens aufgrund der zweifachen Auslese noch ungünstiger. Ein in [94] vorgestellter Hochgeschwindigkeits-CMOS-Bildsensor, der mit einem Photogate-Pixel und einem implementierten CDS-Verfahren realisiert ist, erreicht bei einer Integrationszeit von 75  $\mu$ s durch das verwendete Ausleseverfahren die Bildraten von nur 400 Bilder/s.

In dem hier präsentierten Bildsensor wird das Problem des kritischen Zeitschemas aufgrund der spaltenweise eingesetzten CDS-Stufe mit dem Einsatz einer Sample-and-Hold-Stufe (S/H-Stufe) gelöst, durch die ein versetzter Pipeline-Betrieb bei der Signalauslese gewährleistet wird. Ein solcher Betrieb ermöglicht eine synchrone Auslese der Signale aus der photoempfindlichen Matrix zum Spaltenverstärker und eine Auslese der innerhalb S/H-

Stufe jeder Spalte zwischengespeicherten CDS-gefilterten Signale zu den Sensorausgängen.

Mit einer Unterdrückung des örtlichen und eines relevanten Teiles des zeitlichen Rauschens (1/f-Rauschen) soll mit diesem Schaltungskonzept ein Hochgeschwindigkeits-CMOS-Bildsensor für eine störungsfreie und hochwertige Bildaufnahme gewährleistet werden.

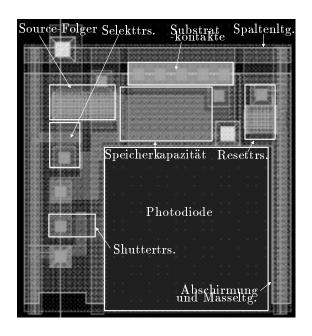

### 5.2.2 Schaltungstechnische Realisierung

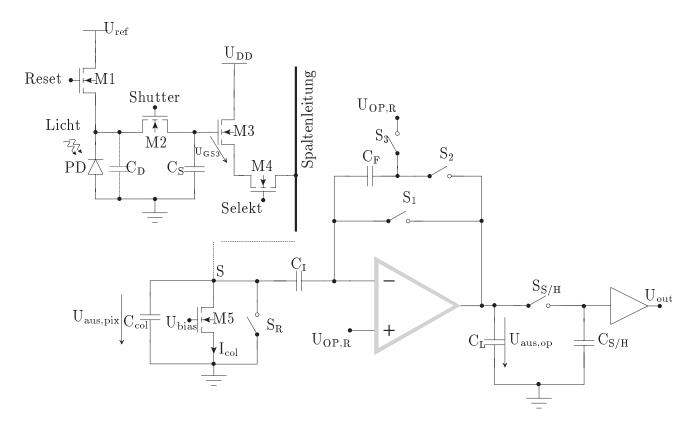

Die Basis dieses CMOS-Bildsensors stellen die in Abbildung 5.10 eingesetzte Pixelstruktur und ein spaltenorganisierter Ausleseverstärker mit einer S/H-Stufe an seinem Ausgang dar. Das verwendete Pixel mit dem elektronischen Shutter im Standard-Modus (siehe Kapitel 4.3.1) nutzt in diesem Konzept einen Source-Folger als Ausgangsverstärker im Pixel. Er dient dazu, die hochkapazitive Spaltenleitung zu treiben, wobei die Spannung an seinem Eingang (am Speicherkondensator  $C_S$ ) fast unverändert an der Spaltenleitung erscheint. Die Funktionsweise des Pixels vor der Auslese, d.h. der Resetvorgang und die mit allen anderen Pixeln durchgeführte synchrone Integration bleiben unverändert. Dabei wird gemäß der Ansteuerung der Transistoren M1 und M2 durch das globale "Reset"- und "Shutter"-Signal (siehe Abbildung 4.9) nach einem Zurücksetzten aller Pixel (Detektorkapazität  $C_D$  und Speicherkapazität  $C_S$  werden auf  $U_{ref}$  aufgeladen) und einer durchgeführten Integration auf beiden Kapazitäten der Speicherkondensator  $C_S$  von der Photodiode enkoppelt. Mit einer so gewonnenen und am Kondensator  $C_S$  abgespeicherten Photospannung  $(U_{pix} = U_{ref} - U_{int})$ kann die Auslese durch das Schließen des Transistors M4 (aller Pixel einer Zeile) beginnen. Während der zeilenweise ablaufenden Auslese der gewonnenen Datensignale werden die Transistoren M1 und M2 durch ein zeilenweise ablaufendes "Reset"- und "Shutter"-Signal geschlossen und das Pixel wird für die Durchführung des CDS-Verfahrens zusätzlich zurückgesetzt (siehe Abbildung 5.11). Die Überlegungen für das eingesetzte Pixel bezüglich der Unterdrückung von Smearing und Blooming bleiben wie beim besprochenen einfachen Pixel mit synchronem elektronischen Shutter (siehe Kapitel 4) gleich.

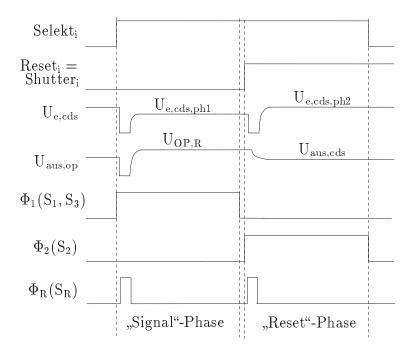

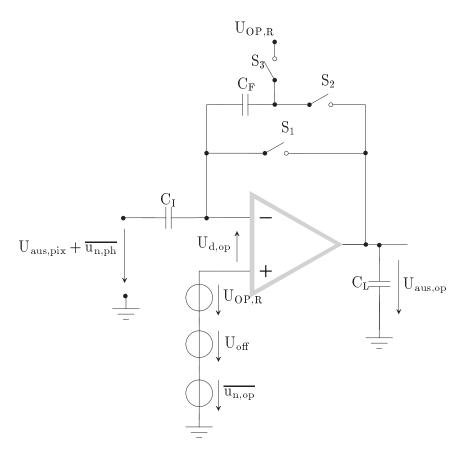

Der Spaltenausleseverstärker ist eine Switched-Capacitor-Schaltung, die ein CDS-Verfahren implementiert. Die Auslese der in den Pixeln ermittelten Spannungen erfolgt nach dem Prinzip des CDSs in zwei Phasen, mit Hilfe der Steuerspannungen gezeigt in Abbildung 5.11. Zuerst werden in der "Signal"-Phase aus den Pixeln einer angewählten Zeile die auf dem Kondensator  $C_S$  gespeicherten Spannungen ausgelesen. Dafür ist mittels des Schalters  $S_R$ , der mit dem Signal  $\Phi_R$  angesteuert wird, zuerst das Potential der Spaltenleitung auf Masse gezogen. Damit kann anschließend der Source-Folger im Pixel die große parasitäre Spaltenkapazität  $C_{col}$ , d.h. den Eingangsknoten des spaltenorientierten Ausleseverstärkers, der das CDS-Verfahren implementiert, auf die Spannung  $U_{e,cds,ph1} = U_{ref} - U_{int} - U_{GS3}$  aufladen. Dabei sind (während der ersten "Signal"-Phase) mittels des Steuersignals  $\Phi_1$  beide Schalter  $S_1$  und  $S_3$  geschlossen bzw. mittels  $\Phi_2$  der Schalter  $S_2$  geöffnet, so daß der Operationsver-

Abbildung 5.10: Das Pixel mit elektronischem Shutter und Spannungsauslese und die S/H-Schaltung.

stärker als ein Eins-Verstärker zurückgekoppelt ist. Dabei lädt sich der Kondensator  $C_I$  auf die Spannung auf, die einer Differenz zwischen dem aus dem Pixel ausgelesenen Signalwert und der Referenzspannung des Operationsverstärkers entspricht  $(U_{e,cds,ph1}-U_{OP,R})$ . In der zweiten "Reset"-Phase wird der Schalter  $S_2$  mit Hilfe seines Steuersignals  $\Phi_2$  geschlossen und  $S_1$  und  $S_3$  werden mit Hilfe von  $\Phi_1$  geöffnet<sup>2</sup>. Nach der zeilenweisen Ansteuerung der Transistoren M1 und M2 seitens des "Reset"- und des "Shutter"-Signals, die während der zeilenweisen Auslese mit Zeilendekoder erzeugt sind, liegt der Resetwert (entspricht der Resetspannung  $U_{ref}$ ) bereit für die Auslese aus dem Pixel vor. Vor seiner Auslese wird allerdings das Potential der Spaltenleitung wiederum über den Schalter  $S_R$  (mit dem Signal  $\Phi_R$ ) auf Masse zurückgesetzt, so daß der Source-Folger anschließend die Spaltenleitung, d.h. den Eingangsknoten des Ausleseverstärkers auf die Spannung  $U_{e,cds,ph2} = U_{ref} - U_{GS3}$  aufladen kann. Damit bildet sich an den Kondensatoren  $C_I$  und  $C_F$  eine Spannung, die der Differenz dieser und der Referenzspannung des Operationsverstärkers  $U_{e,cds,ph2} - U_{OP,R}$  entspricht. Wenn man annimmt, daß die Verstärkung des Operationsverstärkers unendlich groß ist, ergibt sich aufgrund der Ladungserhaltung am negativen Eingang des Operationsverstärkers

<sup>&</sup>lt;sup>2</sup>Der Einsatz des Schalters  $S_3$  für eine Auto-Korrektur der Offsetspannung des Operationsvestärkers wird nachträglich erklärt.

Abbildung 5.11: Zeitschema der Steuersignale für die korrelierte Doppelabtastung (CDS), angewendet auf aller Pixel *i*-ter Zeile.

für die beiden zu berücksichtigenden Auslesephasen (s. Abbildung 5.11) folgende Beziehung

$$Q_{cds,ph1} = C_I (U_{OP,R} - U_{e,cds,ph1}) =$$

$$= C_I (U_{OP,R} - U_{e,csd,ph2}) + C_F (U_{aus,op} - U_{OP,R}) = Q_{cds,ph2},$$

(5.26)

wobei  $U_{aus,op}$  die Ausgangsspannung des Operationsverstärkers darstellt. Wird Gleichung (5.26) nach dieser Ausgangsspannung aufgelöst, die nach dem Abschluß der "Reset"-Phase den endgültigen Wert der CDS-gefilterten Spannung  $U_{aus,cds}$  annimmt, ergibt sich der folgende Ausdruck

$$U_{aus,op} = U_{aus,cds} = (U_{e,cds,ph1} - U_{e,cds,ph2}) \frac{C_I}{C_F} + U_{OP,R}.$$

(5.27)

Wie der Gleichung (5.27) zu entnehmen ist, entspricht die Ausgangsspannung des Operationsverstärkers einer Differenz der zwei aus dem Pixel ausgelesenen Werte, die während der Zeit  $T_{zeile}$ , in der eine Zeile angewählt ist, reduziert um die Abtastzeit der S/H-Stufe ausgelesen werden müssen. Neben den beschriebenen Steuersignalen, die für den richtigen Betrieb dieser Schaltung notwendig sind, sind in Abbildung 5.11 prinzipielle Verläufe des Signals am Eingang  $U_{e,cds}$  und am Ausgang  $U_{aus,op}$  der CDS-Schaltung (Ausgang des Operationsverstärker) ebenso präsentiert.

Nachdem die "Reset"-Phase der beschriebenen Auslese abgeschlossen ist, liegt am Ausgang des Operationsverstärkers die durch Gleichung (5.27) beschriebene CDS-gefilterte Spannung  $U_{aus,op}$  für die weitere Auslese bereit. Diese Spannung wird anschließend innerhalb

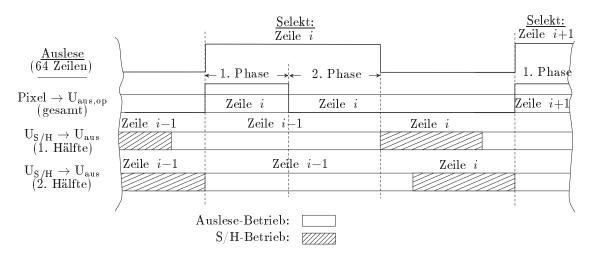

jeder Spalte mittels des Schalters  $S_{S/H}$  abgetastet und auf dem Kondensator  $C_{S/H}$  gespeichert. Damit liegt das CDS-gefilterte Signal für die Auslese am Ausgang des ICs bereit. (Wird wie bisher die Signalauslese innerhalb einer Spalte betrachtet, dürfen während dieses Abtastvorgangs weder neue Werte aus dem Pixel noch vom Kondensator  $C_{S/H}$  nach außen ausgelesen werden.) Die Signalauslese aus allen Pixeln der Zeile i zum Ausgang des dazugehörigen Spalten-Operationsverstärkers findet synchron mit der Auslese der aus Zeile i-1 an den Speicherkondensatoren  $C_{S/H}$  gespeicherten und zuvor CDS-gefilterten Pixelwerte zum Sensorausgang statt. Dieser für kurze Bilddauern (und somit hohe Bildraten) entscheidende versetzte Pipelinebetrieb ist in Abbildung 5.12 für einen der vier Ausgangskanäle (siehe später die Sensorarchitektur) mit den zugehörigen 64 Spalten gezeigt.

Abbildung 5.12: Zeitschema der synchronen Auslese im versetzten Pipelinebetrieb.

Während die Zeile i angewählt ist, findet in der ersten Phase die Auslese der Signale aus den angesprochenen Pixeln zu den Kondensatoren  $C_I$  statt. Gleichzeitig werden die zuvor an den Kondensatoren  $C_{S/H}$  gespeicherten CDS-gefilterten Signalwerte aus der Zeile i-1 in einem versetzten Modus zum Sensorausgang ausgelesen. Diese Auslese zum Sensorausgang findet auch während der zweiten Phase der Auslese der Signale aus den Pixeln zu den Ausgängen der Spalten-Operationsverstärker statt. (In der zweiten Phase werden die Resetwerte aus den Pixeln, notwendig für das CDS-Verfahren, ausgelesen und die notwendige Differenz gebildet). Die Auslese der Signale der ersten Hälfte der Spalten (der Zeile i-1) zu dem Sensorausgang endet vor der jeweiligen Auslese der zweiten Hälfte der Spalten im gleichermaßen versetzten Betrieb, so wie die Auslese der beiden Signalgruppen begonnen hat. Anschließend wird die Abtastung und Speicherung der neuen an den Operationsverstärkerausgängen gewonnenen Signale zu den Speicherkondensatoren durchgeführt. Der beschriebene versetzte Pipeline-Ablauf wiederholt sich, bis die Pixel aus der ganzen photoempfindlichen Matrix zeilenweise ausgelesen sind. Mit diesem Ausleseprinzip ist eine schnelle Auslese mit implementiertem CDS-Verfahren für hohe Bildraten gewährleistet.

# 5.2.3 Statische Übertragungsfunktion und "Matching"-Verhalten

In der zuvor beschriebenen Funktionalität der Schaltung wurden keine Einflüsse des örtlichen und des zeitlichen Rauschens sowie die Unvollkommenheit des Operationsverstärkers durch seine endliche Verstärkung (und Offset-Spannung) auf die Übertragungsfunktion berücksichtigt. Um die Problematik der Spannungsauslese sowie eine Unterdrückung der parasitären Effekte durch das CDS-Verfahren zu verstehen, wird auf die Ursache dieser Effekte näher eingegangen.

Zuerst wird die Übertragungsfunktion bis zum Eingang der CDS-Schaltung berücksichtigt werden. Unter Berücksichtigung der Geometrie  $W_3$   $L_3$  und des Verstärkungsfaktors  $\beta_3$ , sowie des Substrat-Effekts [77] des Source-Folgers M3 kann für die Ausgangsspannung des Pixels  $U_{aus,pix}$ , die gleichzeitig die Eingangsspannung der CDS-Schaltung  $U_{e,cds}$  darstellt, folgendes geschrieben werden

$$U_{aus,pix} = U_{ref} - U_{int} - U_{t,3} - \sqrt{\frac{2 L_3}{\beta_3 W_3}} I_{col} + \gamma \sqrt{2 U_F} - \sqrt{\left(-\frac{1}{2} + \frac{1}{2}\sqrt{4 (U_{ref} - U_{int}) - 4 U_{t,3} - 4 \sqrt{\frac{2 L_3}{\beta_3 W_3}} + 4 \gamma \sqrt{2 U_F} + 8 U_F + \gamma^2\right)}.$$

(5.28)

wobei der Term  $U_{t,3} + \sqrt{\frac{2 L_3}{\beta_3 W_3}} I_{col}$  der Spannung  $U_{GS3}$  und der letzte Term dem Einfluß des Substrat-Effekts auf die Schwellenspannung  $U_{t,3}$  entsprechen. In Anbetracht der Technologieparameter des verwendeten 1  $\mu$ m CMOS-Prozesses läßt sich einfach zeigen, daß der Substrat-Effekt eine geringfügig kleinere Verstärkung als Eins hat, aber gleichzeitig eine deutlich geringere Nichtlinearität als die Kapazität der Photodiode verursacht [71]. Infolge dessen kann durch eine Vernachlässigung dieses Effekts für die Ausgangsspannung am Ende der Spaltenleitung unter Berücksichtigung der Kennlinie des Stromquellentransistors M5 bzw. seiner Geometrie  $W_5$   $L_5$ , der Schwellenspannung  $U_{t,5}$ , des Verstärkungsfaktors  $\beta_5$  und der notwendigen Biasspannung  $U_{bias}$  geschrieben werden

$$U_{aus,pix} = U_{ref} - U_{int} - U_{t,3} - \sqrt{\frac{2 L_3}{\beta_n W_3}} I_{col} =$$

$$U_{ref} - \frac{\mathcal{R} A_D E T_{int}}{C_D + C_S} - U_{t,3} - \sqrt{\frac{W_5 L_3 \beta_p}{L_5 W_3 \beta_n}} (U_{bias} - U_{t,5}).$$

(5.29)

Die Ausgangsspannung des Pixels in Gleichung (5.29) bezieht sich auf den Fall, daß nur der

Signalwert ("Signal"-Phase des im vorherigen Unterkapitel beschriebenen CDS-Verfahrens) aus dem Pixel ausgelesen wird oder daß es sich dabei um eine Auslese ohne CDS-Verfahren handelt. Um für diesen Fall das gesamte örtliche Rauschen zu ermitteln, das sich der Signalinformation bei der Auslese aus den Pixeln überlagert, muß aus Gleichung (5.29) unter Berücksichtigung der "Matching"-Eigenschaften der eingesetzten Transistoren bzw. der Varianzen aller unabhängigen Anteile [67] die Varianz der Ausgangsspannung gemäß Gleichung (5.6) berechnet werden. Wenn der Einfluß der örtlichen Schwankungen des Dunkelstroms  $I_{dark}$  eingeschlossen werden soll, wird zuvor die Spannung  $U_{int}$  in Gleichung (5.29) gemäß Gleichung (5.5) erweitert, so daß sich schließlich die Varanz der Ausgangsspannung zu folgendem ergibt

$$\sigma_{u,a,s}^{2} = \left(\frac{\overline{L_{3}}}{2\overline{W_{3}}\overline{\beta_{3}}}\overline{I_{col}}\right) \sum_{i=3,5} \left(\frac{\sigma_{L,i}^{2}}{\overline{L_{i}}^{2}} + \frac{\sigma_{W,i}^{2}}{\overline{W_{i}}^{2}} + \frac{\sigma_{\beta,i}^{2}}{\overline{\beta_{i}}^{2}}\right) + \sigma_{u,t,3}^{2} + \frac{\overline{W_{5}}\overline{L_{3}}\overline{\beta_{5}}}{\overline{L_{5}}\overline{W_{3}}\overline{\beta_{3}}}\sigma_{u,t,5}^{2} + \left(\frac{T_{int}}{C_{D} + C_{S}}\right)^{2} \sigma_{dark}^{2} + \left(\overline{U_{int}}^{2} + \overline{U_{dark}}^{2}\right) \left[\frac{\sigma_{CD}^{2} + \sigma_{CS}^{2}}{\left(C_{D} + C_{S}\right)^{2}}\right].$$

$$(5.30)$$

Weil der Einfluß von Prozeßschwankungen auf die Kapazitätsgrößen der Kondensatoren im Pixel aufgrund der Größe der Kapazitäten vernachlässigt werden kann, besitzt das örtliche Rauschen nur eine signalunabhängige (additive) Komponente. Aufgrund dessen räumt das verwendete Pixel mit einem Source-Folger in Kombination mit der eingesetzten Stromquelle die Möglichkeit für einen effizienten Einsatz des CDS-Verfahrens ein.

Neben dem Einfluß der Prozeßschwankungen auf das gerade beschriebene FPN im Signal am Pixelausgang bzw. an dem Eingang der CDS-Schaltung, wird eine weitere Komponente des FPN in der gesamten Schaltung zwischen den Spalten durch die Offsetspannungen der Operationsverstärker verursacht, die aufgrund einer endlichen Verstärkung  $A_0$  der Operationsverstärker entstehen.

Um die Wirkung des CDS-Verfahrens auf alle Komponenten des existierenden FPNs zu verdeutlichen, ist die CDS-Schaltung in Abbildung 5.13 mit einem Operationsverstärker endlicher Verstärkung  $A_0$ , seiner Offsetspannung  $U_{off}$  und seiner modellierten Eingangsrauschquelle  $\overline{u_{n,op}^2}$  dargestellt. Die Eingangsspannung während der (ersten) "Signal"-Phase  $U_{e,cds,ph1}$  entspricht der Spannung  $U_{aus,pix}$  aus Gleichung (5.29), die um die zeitliche (siehe später) und örtliche (siehe Gleichung (5.30)) Rauschspannung (gemeinsam dargestellt:  $\overline{u_{n,ph1}}$ ) erweitert ist. Ähnlich entspricht die Eingangsspannung während der (zweiten) "Reset"-Phase  $U_{e,cds,ph2}$  der Spannung  $U_{aus,pix}$  aus Gleichung (5.29) für  $U_{int} = 0 V$ , die ebenso um die zeitliche (siehe später) und örtliche (siehe Gleichung (5.30) für ebenso  $U_{int} = 0 V$ ) Rauschspannung (gemeinsam dargestellt:  $\overline{u_{n,ph2}}$ ) ergänzt ist.

<sup>&</sup>lt;sup>3</sup>Die Bandbreite des Operationsverstärkers ist für die folgenden Überlegungen als unendlich groß angenommen worden  $f_{3dB} \to \infty$ .

Abbildung 5.13: Schaltung zur Realisierung des CDS-Verfahrens mit den zugehörigen Rauscheinflüssen.

$$U_{e,cds,ph1} = U_{ref} - U_{sig} - U_{t,3} - \sqrt{\frac{W_5 L_3 \beta_p}{L_5 W_3 \beta_n}} \left( U_{bias} - U_{t,5} \right) + \overline{u_{n,ph1}}$$

$$U_{e,cds,ph2} = U_{ref} - U_{t,3} - \sqrt{\frac{W_5 L_3 \beta_p}{L_5 W_3 \beta_n}} \left( U_{bias} - U_{t,5} \right) + \overline{u_{n,ph2}}.$$

(5.31)

Wenn wiederum die Ladungserhaltung am negativen Eingangsknoten des Operationsverstärkers für sowohl die "Signal"-Phase  $(\Phi_1(S_1, S_3) = 1 \text{ und } \Phi_2(S_2) = 0)$  als auch die "Reset"-Phase  $(\Phi_1(S_1, S_3) = 0 \text{ und } \Phi_2(S_2) = 1)$  berücksichtigt wird, kann die folgende Gleichung aufgestellt werden:

$$Q_{cds,ph1} = C_{I} \left( -U_{d1,op} + U_{OP,R} + U_{off} + \overline{u_{n,ph1,op}} - U_{e,cds,ph1} \right) +$$

$$C_{F} \left( -U_{d1,op} + U_{off} + \overline{u_{n,ph1,op}} \right) =$$

$$= C_{I} \left( -U_{d2,op} + U_{OP,R} + U_{off} + \overline{u_{n,ph2,op}} - U_{e,cds,ph2} \right) +$$

$$C_{F} \left( -U_{d2,op} + U_{OP,R} + U_{off} + \overline{u_{n,ph2,op}} - U_{aus,op} \right) = Q_{cds,ph2}.$$

(5.32)

Dabei ist die differenzielle Spannung am Eingang des Operationsverstärkers in der ersten Phase  $U_{d1,op} = \frac{1}{1+A_0} U_{off}$  für den Fall eines Eins-Verstärkers bzw. in der zweiten Phase  $U_{d2,op} = \frac{1}{A_0} U_{aus}$  für den Fall eines großsignalmäßigen Leerlauf-Verstärkers. Wenn die Gleichung (5.32) nach der Ausgangsspannung  $U_{aus}$  aufgelöst wird, ergibt sich ein Ausdruck von

$$U_{aus,op} = \frac{A_0 C_F}{(1 + A_0) C_F + C_I} U_{OP,R} + \frac{A_0}{(1 + A_0) C_F + C_I} \cdot \left[ C_I \left( U_{e,cds,ph1} - U_{e,cds,ph2} \right) + \left( C_F + C_I \right) \frac{U_{off}}{1 + A_0} + \left( C_F + C_I \right) \left( \overline{u_{n,ph2,op}} - \overline{u_{n,ph1,op}} \right) \right].$$

$$(5.33)$$

Werden in Gleichung (5.33) die Spannungen  $U_{e,cds,ph1}$  und  $U_{e,cds,ph2}$  aus Gleichung (5.31) eingesetzt, ergibt sich mit den Bedingungen  $A_0 \gg 1$  und  $A_0 C_F \gg C_I$  die Ausgangsspannung zu

$$U_{aus,op} = U_{OP,R} - \frac{C_I}{C_F} U_{int} + \left(1 + \frac{C_I}{C_F}\right) \frac{U_{off}}{1 + A_0} + \frac{C_I}{C_F} \left(\overline{u_{n,ph1}} - \overline{u_{n,ph2}}\right) + \left(1 + \frac{C_I}{C_F}\right) \left(\overline{u_{n,ph2,op}} - \overline{u_{n,ph1,op}}\right).$$

(5.34)

Wie der Gleichung (5.34) aus den Termen  $\frac{C_I}{C_F} \left( \overline{u_{n,ph1}} - \overline{u_{n,ph2}} \right)$  und  $\left( 1 + \frac{C_I}{C_F} \right) \left( \overline{u_{n,ph2,op}} - \overline{u_{n,ph1,op}} \right)$ zu entnehmen ist, läßt sich mit dem CDS-Verfahren ein signalunabhängiges (additives) FPN durch gegebene Differenz beheben. Außerdem kann mit dem Einsatz des Schalters S3 die Offsetspannung für eine ausreichend hohe Verstärkung  $A_0$  jedes einzelnen Operationsverstärkers unterdrückt werden  $\left(\left(1+\frac{C_I}{C_F}\right) \xrightarrow{U_{off}} 0\right)$ . Ferner ermöglicht das CDS-Verfahren, wie im vierten Kapitel beschrieben, eine teilweise Unterdrückung des zeitlichen Rauschens. Für das zeitliche Rauschen ergeben sich gemäß der letzten zwei Terme aus Gleichung (5.34) folgende Überlegungen: für das niederfrequente Rauschen korrelieren die Rauschanteile der (ersten) "Signal"- und (zweiten) "Reset"-Phase, so daß aufgrund der gegebenen Differenz dieses Rauschen unterdrückt wird. Dagegen sind die Rauschanteile der (ersten) "Signal"- und (zweiten) "Reset"-Phase für höhere Frequenzen unkorreliert und es kommt zur Erhöhung des hochfrequenten Rauschens. Aufgrund der Unabhängigkeit dieser Rauschanteile werden ihre Rauschleistungen (Varianzen) addiert, so daß sich der Rauschbeitrag (d.h. Rauschspannung) des Pixels sowie der Rauschbeitrag des Operationsverstärkers bei der CDS-Schaltung (verglichen mit der Schaltung, deren Auslese nur aus der "Signal"-Phase bestünde) um den Faktor  $\sqrt{2}$  erhöht. Als Fazit gilt folgendes: für die bevorstehende Rauschanalyse wird das 1/f-Rauschen aufgrund der beschriebenen Tatsachen bzw. der deutlich geringeren Anzahl der Dekaden (siehe Kapitel 4) in der gesamten Rauschbilanz der eingesetzten Schaltung aus Abbildung 5.10 vernachlässigt. Dagegen wird das weiße Rauschen in beiden Phasen separat betrachtet und schließlich seine Rauschleistungen für die gesamte Rauschbilanz aufaddiert.

#### 5.2.4 Rauschverhalten

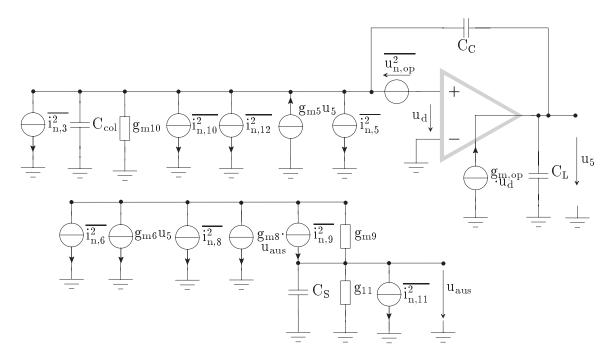

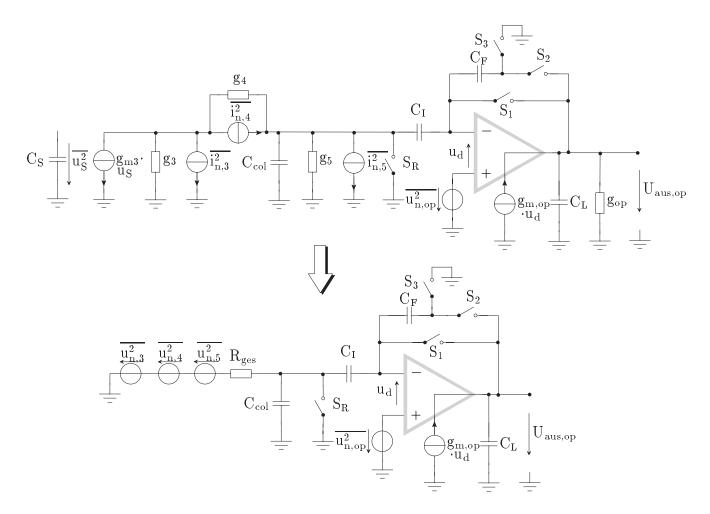

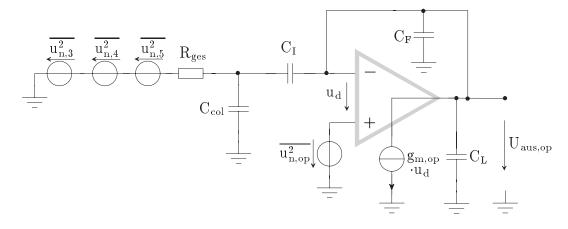

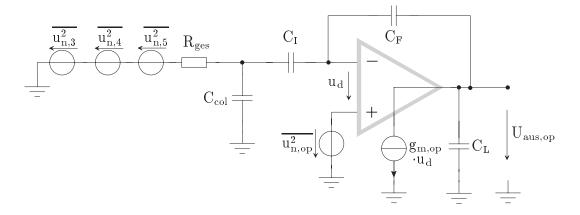

Für die Berechnung des Rauschens der verwendeten Schaltung aus Abbildung 5.10 wird wiederum auf das im vierten Kapitel beschriebene Rauschverhalten im Pixel, d.h. auf sein kTC-, Dunkelstrom- und Photonenrauschen zurückgegriffen. Für den Rest der Schaltung wird gemäß der zuvor beschriebenen Natur des CDS-Verfahrens das 1/f-Rauschen vernachlässigt, bzw. das erhöhte weiße Rauschen für beide Auslesephasen berücksichtigt und entsprechend aufaddiert. Ein der zu untersuchenden Schaltung entsprechendes Rauschersatzschaltbild ist in Abbildung 5.14 gezeigt. Bei dem Operationsverstärker sowie allen in Sättigung funktionierenden Transistoren bis auf den Stromquellentransistor M5 kann der Ausgangsleitwert gegenüber der Transkonduktanz vernachlässigt werden  $(g_{m,op} \gg g_{op}$  und  $g_{m3} \gg g_3)$ . Bei M5 gilt hingegen  $g_5 \gg g_{m5}$ . Zusätzlich werden noch die Transkonduktanz  $g_{m3}$  des Transistors M3 und die Ausgangsleitwerte  $g_4$  und  $g_5$  der Transistoren M4 und M5 respektive zu einem Widerstand  $R_{ges}$  zusammengefaßt. Dementsprechend kann sein Leitwert wie folgt geschrieben werden:

$$g_{ges} = \frac{1}{R_{ges}} = (\frac{1}{g_{m3}} + \frac{1}{g_4}) \| \frac{1}{g_5} \approx \frac{g_{m3} g_4}{g_{m3} + g_4},$$

(5.35)

wobei die durchgeführte Annäherung aufgrund des kleinen Ausgangsleitwertes  $g_5$  der Stromquelle M5 gerechtfertigt ist.

Die Rauschleistungsdichten der Spannung der für das Rauschen relevanten Bauelemente betragen

$$S_{u,3,5}(f) = \frac{8}{3} k T \frac{1}{g_{m3,5}} + \frac{k_f}{C'_{ox} W_{3,5} L_{3,5} f}$$

$$S_{u,4}(f) = 4 k T \frac{1}{g_4} + \frac{k_f}{C'_{ox} W_4 L_4 f}$$

$$S_{u,op}(f) = \frac{16}{3} k T \frac{1}{g_{m,op}} + \frac{2 k_f}{C'_{ox} W_{op} L_{op} f},$$

(5.36)

wobei  $W_j|_{j=3,4,5}$ ,  $L_j|_{j=3,4,5}$ , und  $g_j|_{j=m3,4,5}$  als Kanalbreite, Kanallänge und Steilheit des Transistors j bzw.  $W_{op}$ ,  $L_{op}$  und  $g_{m,op}$  als Kanalbreite, Kanallänge und Steilheit des Eingangstransistors des Operationsverstärkers zu bezeichnen sind. Die Berechnung des relevanten weißen Rauschens erfolgt, indem im Unterschied zu der Schaltung aus Abbildung 5.13 die einpolige Übertragungscharakteristik des Operationsverstärkers (durch seine Steilheit  $g_{m,op}$  und dominante Polstelle  $g_{m,op}/C_L$ ) berücksichtigt wird. Dabei werden die durch die Transistoren M3, M4 und M5 am Knoten S verursachten Rauschspannungen  $\sqrt{u_{n,3,4,5,Sig}^2}$

Abbildung 5.14: Das Rauschsignalersatzschaltbild der Spannungsausleseschaltung mit CDS und seine Vereinfachung (unten).

und  $\sqrt{u_{n,3,4,5,Rst}^2}$  (vergleiche den Eingangsknoten der CDS-Schaltung in Abbildung 5.13) sowie die durch den Operationsverstärker an seinem negativen Eingangsknoten verursachten Rauschspannungen  $\sqrt{u_{n,op,Sig}^2}$  und  $\sqrt{u_{n,op,Sig}^2}$  für beide Phasen berechnet. Anschließend wird für diese Rauschquellen die gesamte Leistung des weißen Rauschens am Ausgang  $\overline{u_{n,out,weiß}^2}$  durch eine Summation der einzelnen Rauschleistungen gemäß Formel (5.34) wie folgt ermittelt:

$$\overline{u_{n,out,weiß}^2} = \left(\frac{C_I}{C_F}\right)^2 \left(\overline{u_{n,3,4,5,Sig}^2} + \overline{u_{n,3,4,5,Rst}^2}\right) + \left(1 + \frac{C_I}{C_F}\right)^2 \left(\overline{u_{n,op,Sig}^2} + \overline{u_{n,op,Rst}^2}\right)$$

(5.37)

Es ist noch mal zu betonen, daß die Rauschanteile, die auf das 21/f-Rauschen zurückzuführen sind, vernachlässigt werden. Anschließend werden die Beiträge des kTC-Rauschens, die durch die Schaltvorgänge der Schalter  $S_R$ ,  $S_1$ ,  $S_2$ ,  $S_3$  und  $C_{S/H}$  ausgelöst sind, ermittelt. Im folgenden wird für das weiße Rauschen zwischen den zwei Auslesephasen unterschieden.

#### "Signal"-Phase

Ein für die Signalauslese geltendes Rauschersatzschaltbild ist unter Berücksichtigung der zu dieser Phase passenden Schalterzuständen (Operationsverstärker ist als ein Einsverstärker zurückgekoppelt) und allen relevanten Rauschquellen in Abbildung 5.15 gezeigt.

Abbildung 5.15: Das Rauschsignalersatzschaltbild der Schaltung für die Signalauslese.

Um den Rauscheinfluß der Transistoren M3, M4 und M5 am Knoten S zu ermitteln, wird zuerst die Übertragungsfunktion dieser Rauschquellen für die gesamte Schaltung berechnet. Während die parasitäre Spaltenkapazität  $C_{col}$  und die für gutes Rauschverhalten notwendige Lastkapazität  $C_L$  in der gleichen Größenordnung liegen und gleichzeitig des Kapazitätsverhältnis  $C_{col}$ ,  $C_L \gg C_F$ ,  $C_I$  gilt ( $C_L$  und  $C_I$  sind aufgrund der später erklärten Minimierung des Rauschens des Operationsverstärkers ebenso gleicher Größenordnung), errechnet sich diese Übertragungsfunktion zu

$$H_{3,4,5,Sig}(s) = \frac{s \frac{C_I}{g_{m,op}}}{\left(1 + s \frac{C_{col}}{g_{ges}}\right) \left(1 + \frac{C_I + C_L}{g_{m,op}}\right)}.$$

(5.38)

Aufgrund der geltenden Kapazitätsverhältnisse und da  $g_{m,op} \gg g_{m8}$  gilt, resultiert aus obiger Gleichung ein einpoliger Charakter der Übertragungsfunktion der betrachteten Transistoren M3, M4 und M5 zum Knoten S mit der Polstelle  $g_{ges}/C_{col}$ . Daraus ergibt sich unter Berücksichtigung der dazugehörigen Spektralleistungsdichten nach der Integration über das gesamte Spektrum gemäß der Gleichung (5.10) die gesuchte Rauschleistung des weißen Rauschens am Knoten S zu

$$\overline{u_{n,3,4,5,Sig}^2} = \frac{kT}{C_{col}} \left( \frac{2 g_{ges}}{3 g_{m3}} + \frac{g_{ges}}{g_4} + \frac{2 g_{ges}}{3 g_{m5}} \right),$$

(5.39)

Der als Einsverstärker geschaltete einpolige Operationsverstärker erzeugt in Anbetracht der vorhandenen Kapazitätsverhältnisse  $C_L \gg C_I$ ,  $C_F$  an seinem negativen Eingangsknoten eine mittlere quadratische Rauschspannung des weißen Rauschens von

$$\frac{\overline{u_{n,op,Sig}^2}}{= \frac{4}{3} \frac{k T}{C_L}.$$

(5.40)

Für die Untersuchung des gesamten Rauschens bei der "Signal"-Phase sind aus vorher angegebenen Gründen keine 1/f-Rauschanteile berücksichtigt.

#### "Reset"-Phase

Abbildung 5.16: Das Rauschsignalersatzschaltbild der Schaltung für die Resetauslese.

Analog zu obigen Berechnungen werden die Anteile der beitragenden Rauschleistungen bei der "Reset"-Phase untersucht. Ein der "Reset"-Phase entsprechendes Rauschersatzschaltbild ist in Abbildung 5.16 gezeigt. Mit der gleichen Annahme über die Kapazitätsverhältnisse wie zuvor berechnet sich die Übertragungsfunktion für die rauschenden Transistoren M3, M4 und M5 zum Ausgang der Schaltung als

$$H_{3,4,5,Rst}(s) = -\frac{C_I}{C_F} \frac{1 - s \frac{C_I}{g_{m,op}}}{\left(1 + \frac{C_I(C_F + C_L) + C_F C_L}{g_{m,op} C_F}\right)} \frac{1}{\left(1 + s \frac{C_{col}}{g_{ges}}\right)}.$$

(5.41)

Hieraus läßt sich einfach zeigen, daß die Übertragungsfunktion der Transistoren M3, M4 und M5 zum betrachteten Knoten S den gleichen einpoligen Charakter mit der Polstelle  $g_{ges}/C_{col}$  besitzt. Daher gilt für die quadratische Rauschspannung des weißen Rauschens am Eingangsknoten der CDS-Schaltung (am Knoten S)

$$\overline{u_{n,3,4,5,Rst}^2} = \overline{u_{n,3,4,5,Sig}^2} = \frac{kT}{C_{col}} \left( \frac{2 g_{ges}}{3 g_{m3}} + \frac{g_{ges}}{g_4} + \frac{2 g_{ges}}{3 g_{m5}} \right). \tag{5.42}$$

Für den Rauschbeitrag des Operationsverstärkers bei der "Reset"-Phase errechnet sich nach der Integration seiner ermittelten Übertragungsfunktion mit der Rauschleistungsdichte über das gesamte Frequenzspektrum an seinem negativen Eingangsknoten eine Rauschleistung von

$$\overline{u_{n,op,Rst}^2} = \frac{4}{3} \frac{C_F k T}{C_I C_F + C_L (C_F + C_I)}.$$

(5.43)

Das gesamte weiße Rauschen am Ausgang der Schaltung  $\overline{u_{n,out,weiß}^2}$  nach dem abgeschlossenen CDS-Verfahren (inklusive "Signal"- und "Reset"-Phase) beträgt gemäß Gleichung (5.34) unter Berücksichtigung der Rauschbeiträge aus Gleichungen (5.39), (5.40), (5.43) und (5.44)

$$\overline{u_{n,out,weiß}^{2}} = \left(\frac{C_{I}}{C_{F}}\right)^{2} \frac{2 k T}{C_{col}} \left(\frac{2 g_{ges}}{3 g_{m3}} + \frac{g_{ges}}{g_{4}} + \frac{2 g_{ges}}{3 g_{m5}}\right) + \left(1 + \frac{C_{I}}{C_{F}}\right)^{2} \left(\frac{4}{3} \frac{k T}{C_{L}} + \frac{4}{3} \frac{k T C_{F}}{C_{I} C_{F} + C_{L} (C_{F} + C_{I})}\right)$$

(5.44)

Das 1/f-Rauschen wird, so wie schon bei der "Signal"-Phase, auch für "Reset"-Phase vernachlässigt und kann damit auch bei der Ermittlung der Rauschbilanz der gesamten Schaltung ausgelassen werden.

Die kTC-Rauschbeiträge, die durch die Funktionsweise der eingesetzten Schalter verursacht werden, werden für eine gesamte Zeilenauslese den Steuersignalen der verwendeten Schalter in Abbildung 5.11 folgend näher erläutert. Mit dem Schließen von Schalter  $S_R$  werden die Ladungsfluktuationen aufgrund des thermischen Rauschens seines Innenwiderstands ausgelöst und bei seinem Öffnen an den Kapazitäten  $C_{col}$  und  $C_I$  mit einer mittleren Rauschladung  $\overline{Q_{n,kTC,S_R}} = \sqrt{kT\left(C_{col} + C_I\right)}$  abgespeichert. Dies geschieht sowohl in der "Signal"- als auch in der "Reset"-Phase, so daß sich am Ausgang der Schaltung (unter Berücksichtigung von  $C_{col} \gg C_I$ ) folgende Rauschleistung ergibt

$$\overline{u_{n,out,S_R}^2} = 2 \frac{k T}{C_{col}} \left(\frac{C_I}{C_F}\right)^2. \tag{5.45}$$

Ahnlich verursacht das thermische Rauschen des Innenwiderstands des während der "Signal"-Phase geschlossenen Schalters  $S_1$  Ladungsfluktuationen, die nach dem Phasenwechsel (Schalter  $S_1$  wird eröffnet) auf dem Eingangsknoten des Operationsverstärkers mit einer mittleren Rauschladung  $\overline{Q_{n,kTC,S_1}} = \sqrt{kT(C_I + C_F)}$  abgespeichert werden. Beim geschlossenen Schalter  $S_3$  entstehen während der "Signal"-Phase Rauschfluktuationen mit einer mittleren Rauschladung  $\overline{Q_{n,kTC,S_3}} = \sqrt{kTC_F}$ , die nach dem Phasenwechsel an der Kapazität  $C_F$  gespeichert bleiben. Diese gespeicherten durch die Schalter  $S_1$  und  $S_3$  verursachten Rauschladungen erscheinen am Ausgang des Operationsverstärkers mit folgender Rauschleistung

$$\frac{\overline{u_{n,out,S_1}^2}}{\overline{u_{n,out,S_3}^2}} = \frac{k T C_I}{C_F^2} + \frac{k T}{C_F}, \text{ und}$$

$$\frac{\overline{u_{n,out,S_3}^2}}{\overline{U_{n,out,S_3}^2}} = \frac{k T}{C_F}.$$

(5.46)

Während der Schalter  $S_2$  zur gesamten Rauschleistung mit seinem kTC-Rauschen als

$$\overline{u_{n,out,S_2}^2} = \frac{kT}{C_L},\tag{5.47}$$

beiträgt, verursacht die S/H-Stufe, erst nachdem das CDS-gefilterte Signal gewonnen wurde, während seiner Übertragung zum Ausgang einen zusätzlichen kTC-Rauschterm wie folgt

$$\overline{u_{n,out,S/H}^2} = \frac{kT}{C_{S/H}}.$$

(5.48)

Um die gesamte ausgangsseitige Rauschleistung zu erschließen, sind noch Beiträge von Rauschen im Pixel für beide Auslesephasen zu berücksichtigen. Für das verwendete Pixel, das im Standard-Modus funktioniert, ist der durch die kTC-Rauschanteile entstandene Rauschbeitrag der quadratischen Rauschspannung am Speicherkondensator  $C_S$  in Gleichung (4.29) gegeben. Diese quadratische Rauschspannung wird mittels Source-Folger (Transistor M3) an der Spaltenleitung gebuffert, so daß sie nach zwei beschriebenen Auslesephasen am Ausgang der Schaltung als

$$\overline{u_{n,out,pix}^2} = \left(\frac{C_I}{C_F}\right)^2 2 k T \left(\frac{1}{C_D/2 + C_S} + \frac{C_D}{C_S} \frac{1}{C_D + C_S}\right)$$

(5.49)

erscheint. Schließlich stellt das Photonenrauschen den dominanten Rauschanteil der gesamten Rauschbilanz dar. Das Photonenrauschen, das durch einfallendes Licht ausgelöst wird,